# 高速 USB 转串口芯片 CH9111

手册

版本: 1.1

<https://wch.cn>

## 1、概述

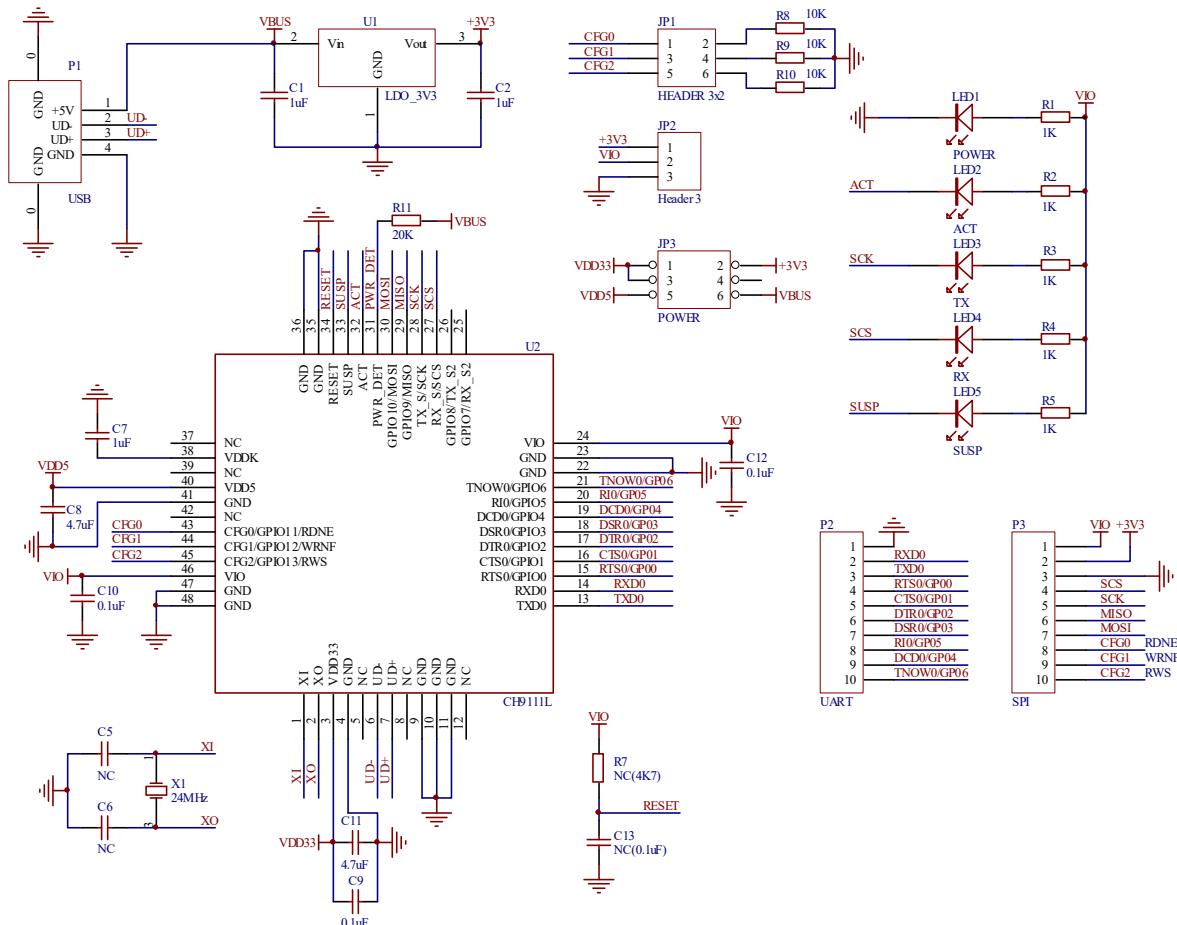

CH9111 是一款高速 USB 2.0 总线的转接芯片，实现高速 USB 转单个异步串口或者异步串口+SPI 同步串行接口功能，用于为计算机扩展异步串口或 SPI 同步串行接口，或者将普通的串口设备或者 MCU 直接升级到 USB 总线。

下图为 CH9111 的系统框图。

图 1-1 系统框图

## 2、特点

- 480Mbps 高速 USB 2.0 设备接口。

- 内置固件，仿真标准串口，用于升级原串口外围设备，或者通过 USB 增加额外串口。

- 计算机端 Windows 操作系统下的串口应用程序完全兼容，无需修改。

- 支持免安装的操作系统内置 CDC 类驱动程序或者多功能高速率的 VCP 厂商驱动程序。

- 硬件全双工串口，内置独立的收发缓冲区，支持通讯波特率 1200bps~15Mbps。

- 串口支持 5/6/7/8 个数据位，支持奇校验、偶校验、标志位、空白位以及无校验。

- 每个串口内置 8192 字节的接收 FIFO，4096 字节的发送 FIFO。

- 支持常用的 MODEM 联络信号 RTS、DTR、DCD、RI、DSR、CTS。

- 支持 CTS 和 RTS 硬件自动流控。

- 支持半双工，提供串口正在发送状态指示 TNOW，可用于控制 RS485 收发切换。

- 支持 USB 虚拟串口与硬件被动 SPI 接口之间双向数据透传功能。

- 支持最多 14 路 GPIO 输入输出功能。

- 通过外加电平转换器件，支持 RS232、RS485、RS422 等接口。

- 内置 EEPROM，可配置芯片 VID、PID、最大电流值、厂商和产品信息字符串等参数。

- 支持 5V 或 3.3V 供电。

- 串口 I/O 独立供电，支持 3.3V、2.5V、1.8V 和 1.2V 电源电压。

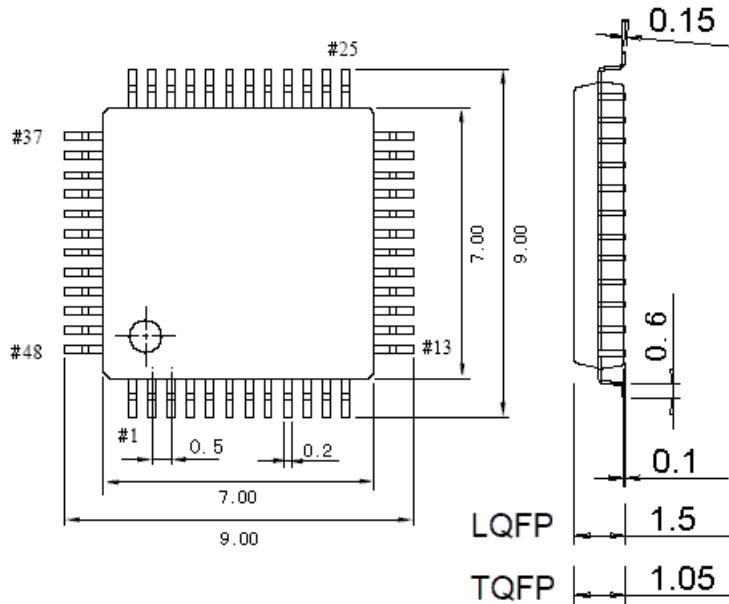

- 提供 LQFP48 无铅封装，兼容 RoHS。

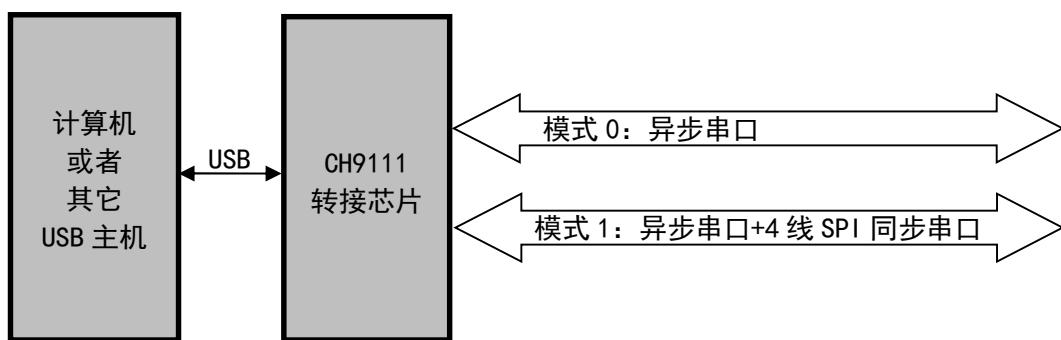

### 3、封装

| 封装形式   | 塑体尺寸  | 引脚节距  |         | 封装说明         | 订货型号    |

|--------|-------|-------|---------|--------------|---------|

| LQFP48 | 7*7mm | 0.5mm | 19.7mil | 标准 LQFP48 贴片 | CH9111L |

注: CH9111 的 USB 收发器按 USB 2.0 全内置设计, UD+和 UD-引脚不能串接电阻, 否则影响信号质量。

### 4、引脚

| 引脚号                                    | 引脚名称           | 类型 <sup>(1)</sup> | 引脚说明                                                                                                                 |

|----------------------------------------|----------------|-------------------|----------------------------------------------------------------------------------------------------------------------|

| 40                                     | VDD5           | P                 | 正电源输入端, 需要外接退耦电容。                                                                                                    |

| 3                                      | VDD33          | P                 | 3.3V 正电源输入端, 需要外接退耦电容。<br>当 VDD5 电压小于 3.6V 时连接 VDD5 输入外部电源,<br>当 VDD5 电压大于 3.6V 时外接退耦电容。                             |

| 4、9、10、11、<br>22、23、35、36、<br>41、47、48 | GND            | P                 | 公共接地端, 需要连接 USB 总线的地线。                                                                                               |

| 38                                     | VDDK           | P                 | 内核电源, 外接至少 0.1uF 退耦电容, 建议 1uF。                                                                                       |

| 24、46                                  | VIO            | P                 | I0 引脚电源输入, 外供 3.3V、2.5V、1.8V 或 1.2V, 外接<br>0.1uF 或 1uF 电容。                                                           |

| 34                                     | RESET          | I                 | 外部复位输入端, 低电平有效, 内置上拉电阻。                                                                                              |

| 7                                      | UD+            | USB               | 直接连到 USB 总线的 D+数据线, 不能额外串接电阻。                                                                                        |

| 6                                      | UD-            | USB               | 直接连到 USB 总线的 D-数据线, 不能额外串接电阻。                                                                                        |

| 1                                      | XI             | I                 | 晶体振荡输入端。                                                                                                             |

| 2                                      | XO             | O                 | 晶体振荡反相输出端。                                                                                                           |

| 13                                     | TXDO           | O                 | UART0 的串行数据输出, 空闲态为高电平。                                                                                              |

| 14                                     | RXDO           | I                 | UART0 的串行数据输入, 内置上拉电阻。                                                                                               |

| 15                                     | RTS0/<br>GPIO0 | I/O               | UART0 的 MODEM 输出信号, 请求发送, 低有效;<br>通用 GPIO0, 用于 I0 口输入或输出。<br>上电期间如果该引脚检测到外接了下拉电阻, 则禁用内部<br>EEPROM 中配置参数, 启用芯片自带默认参数。 |

| 16                                     | CTS0/          | I/O               | UART0 的 MODEM 输入信号, 清除发送, 低有效;                                                                                       |

|    |                          |             |                                                                                                                                                                                      |

|----|--------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | GPIO1                    |             | 通用 GPIO1, 用于 I/O 口输入或输出。                                                                                                                                                             |

| 17 | DTR0/<br>GPIO2           | I/O         | UART0 的 MODEM 输出信号, 数据终端就绪, 低有效;<br>通用 GPIO2, 用于 I/O 口输入或输出。                                                                                                                         |

| 18 | DSR0/<br>GPIO3           | I/O         | UART0 的 MODEM 输入信号, 数据装置就绪, 低有效;<br>通用 GPIO3, 用于 I/O 口输入或输出。                                                                                                                         |

| 19 | DCD0/<br>GPIO4           | I/O         | UART0 的 MODEM 输入信号, 载波检测, 低有效;<br>通用 GPIO4, 用于 I/O 口输入或输出。                                                                                                                           |

| 20 | RIO/<br>GPIO5            | I/O         | UART0 的 MODEM 输入信号, 振铃指示, 低有效;<br>通用 GPIO5, 用于 I/O 口输入或输出。                                                                                                                           |

| 21 | TNOWO/<br>GPIO6          | I/O         | UART0 的 RS485 发送和接收控制引脚;<br>通用 GPIO6, 用于 I/O 口输入或输出。                                                                                                                                 |

| 25 | GPIO7/<br>RX_S2          | I/O         | 模式 0: 通用 GPIO7, 用于 I/O 口输入或输出;<br>模式 1: 串口数据接收状态输出。                                                                                                                                  |

| 26 | GPIO8/<br>TX_S2          | I/O         | 模式 0: 通用 GPIO8, 用于 I/O 口输入或输出;<br>模式 1: 串口数据发送状态输出。                                                                                                                                  |

| 27 | RX_S/<br>SCS             | I/O<br>(FT) | 模式 0: 串口数据接收状态输出;<br>模式 1: 4 线串行 SPI 接口的片选输入。                                                                                                                                        |

| 28 | TX_S/<br>SCK             | I/O<br>(FT) | 模式 0: 串口数据发送状态输出;<br>模式 1: 4 线串行 SPI 接口的时钟输入, 别名 DCK。                                                                                                                                |

| 29 | GPIO9/<br>MISO           | I/O<br>(FT) | 模式 0: 通用 GPIO9, 用于 I/O 口输入或输出;<br>模式 1: 4 线串行 SPI 接口的数据输出, 别名 DOUT 或 SDO。                                                                                                            |

| 30 | GPIO10/<br>MOSI          | I/O<br>(FT) | 模式 0: 通用 GPIO10, 用于 I/O 口输入或输出;<br>模式 1: 4 线串行 SPI 接口的数据输入, 别名 DIN 或 SDI, 内置上拉电阻。                                                                                                    |

| 31 | PWR_DET                  | I<br>(FT)   | USB 总线 VBUS 状态检测输入, 内置下拉电阻。                                                                                                                                                          |

| 32 | ACT                      | 0           | USB 配置完成状态输出, 低电平有效。                                                                                                                                                                 |

| 33 | SUSP                     | 0           | USB 挂起状态输出, 低电平有效, 正常工作状态输出高电平, 挂起后输出低电平。                                                                                                                                            |

| 43 | CFG0/<br>GPIO11/<br>RDNE | I/O<br>(FT) | 功能配置引脚 0。<br>上电期间如果检测到该引脚外接了下拉电阻, 则串口自动使能硬件流控功能;<br>模式 0: 通用 GPIO11, 用于 I/O 口输入或输出;<br>模式 1: SPI 接口数据发送 FIFO 非空状态输出。<br>低电平表示发送 FIFO 有数据可以读取;<br>高电平表示发送 FIFO 无数据可以读取。               |

| 44 | CFG1/<br>GPIO12/<br>WRNF | I/O<br>(FT) | 功能配置引脚 1,<br>上电期间如果检测到该引脚外接了下拉电阻, 则使能芯片模式 1 功能, 否则为模式 0 功能。<br>模式 0: 通用 GPIO12, 用于 I/O 口输入或输出;<br>模式 1: SPI 接口数据接收 FIFO 数据非满状态输出, 低电平表示接收 FIFO 有空间可以写入数据;<br>高电平表示接收 FIFO 无空间可以写入数据。 |

| 45 | CFG2/<br>GPIO13/<br>RWS  | I/O<br>(FT) | 功能配置引脚 2。<br>模式 0: 通用 GPIO13, 用于 I/O 口输入或输出;<br>模式 1: SPI 接口数据读取或写入状态输入。<br>低电平表示当前为读取数据状态;<br>高电平表示当前为写入数据状态。                                                                       |

|                     |    |    |           |

|---------------------|----|----|-----------|

| 5、8、12、37、<br>39、42 | NC | NC | 空脚, 建议悬空。 |

|---------------------|----|----|-----------|

注 1: 引脚类型缩写解释:

USB = USB 信号引脚;

I = 信号输入;

O = 信号输出;

P = 电源或地;

NC = 空脚;

FT = 耐受 5V 电压。

## 5、功能说明

### 5.1 一般说明

CH9111 芯片支持 5V 或者 3.3V 电源电压, 当使用 5V 工作电压 (大于 4.0V) 时, VDD5 引脚输入外部 5V 电源 (例如 USB 总线电源), 由内部电源调节器于 VDD33 引脚产生 3.3V 电源, 用于 USB 收发器, VDD33 引脚应该外接 4.7uF 并 0.1uF 左右的电源退耦电容。当使用 3.3V 或更低工作电压 (小于 3.6V) 时, VDD33 引脚应该与 VDD5 引脚相连接, 同时输入外部的 3.3V 电源, VDD33 引脚仍需外接电源退耦电容。

V10 是除 USB 信号外 I/O 的独立供电引脚, 需外接 0.1uF 或 1uF 对地电容, 支持 3.3V、2.5V、1.8V 和 1.2V 电源电压, V10 应该与 SPI 主机、串口外设使用同一电源供电。

CH9111 芯片内置了电源上电复位电路, 芯片正常工作时需要外部向 X1 引脚提供 24MHz 时钟信号, 时钟信号可通过 CH9111 内置的反相器通过晶体稳频振荡产生。外围电路需要在 X1 和 X0 引脚之间连接一个 24MHz 晶体, 芯片内置的晶体负载电容为 12pF, 如果晶体负载电容超过 20pF, 则可根据晶体需求选择合适的负载电容。

CH9111 芯片推荐使用外部晶体, 如果芯片工作环境相对比较理想, 且串口波特率误差能满足使用需求时, 可以不焊接外置晶体, 将 X1 引脚连接 GND 后, 芯片自动切换使用内置时钟。

CH9111 芯片内置了 USB 总线所需要的所有外围电路, 包括内嵌 USB 控制器和 USB-PHY、USB 信号线的串联匹配电阻、Device 设备所需的 1.5K 上拉电阻等。UD+ 和 UD- 引脚可以直接连接 PC 或其它 USB 主机, 如果为了芯片安全而串接保险电阻或者电感或者 ESD 保护器件, 那么交直流等效串联电阻应该在 5Ω 之内。

### 5.2 工作模式说明

CH9111 芯片在复位时, 通过检测 CFG1 引脚的电平状态配置芯片的工作模式, 工作模式及对应的转接功能如下表。

表 5-1 工作模式及对应的转接功能

| 工作模式   | CFG1 引脚状态 | 芯片功能                                                            | 默认的产品 ID |

|--------|-----------|-----------------------------------------------------------------|----------|

| 工作模式 0 | 悬空或高电平    | USB 转高速单串口,<br>RX_S 和 TX_S 为串口收发数据状态输出引脚                        | 55E9H    |

| 工作模式 1 | 下拉低电平     | USB 转高速串口+ USB 转 4 线 SPI 同步串行接口,<br>RX_S2 和 TX_S2 为串口收发数据状态输出引脚 | 55EAH    |

工作模式 0: USB 转高速单串口, 在计算机上识别为 1 个标准的 USB 串口。串口支持全 MODEM 信号, 支持硬件流控, 支持 RS485 串口收发使能控制。

工作模式 1: USB 转高速串口和 USB 转 4 线 SPI 接口。在计算机上识别为 2 个标准的 USB 串口, 第 1 个串口对应于硬件 UART 接口, 第 2 个串口对应于硬件 SPI 接口, 适用于同时使用串口及 4 线 SPI 同步串行接口的需求。串口支持全 MODEM 信号, 支持硬件流控, 支持 RS485 串口收发使能控制。芯片的 4 线 SPI 接口工作在从机模式, 配合辅助引脚, 接收外部 SPI 主机发送的数据并通过 USB 接口上传,

同时接收 USB 接口下传的数据并通过 SPI 接口发送，实现 USB 虚拟串口和硬件 SPI 接口的数据双向透传功能。

### 5.3 串口说明

CH9111 芯片提供 1 组异步串口 UART0，串口包括 TXD、RXD、RI、DSR、DCD、DTR、CTS 和 RTS 等引脚，可实现 3 线串口、5 线串口或 9 线串口通信。

异步串口方式下 CH9111 芯片的引脚包括：数据传输引脚、MODEM 联络信号引脚和辅助引脚。

数据传输引脚包括：TXD0、RXD0。串口输入空闲时，RXD0 为高电平，串口输出空闲时，TXD0 为高电平。

MODEM 联络信号引脚包括：CTS0、RTS0、DTRO、DCD0、RIO、DSR0。

辅助引脚包括：TNOW0、ACT、SUSP、CFG0、CFG1 和 CFG2 等。TNOW0 为对应串口的 RS485 发送和接收控制引脚。ACT 为 USB 设备配置完成状态输出引脚，上电默认输出高电平，USB 主机对 CH9111 芯片进行 USB 配置后则输出低电平。SUSP 引脚为 USB 挂起状态输出，低电平有效，正常工作状态输出高电平，挂起后输出低电平。CFG0 为功能配置引脚 0，上电期间如果检测到该引脚外接了下拉电阻，则串口自动使能硬件流控功能。TX\_S/TX\_S2 为芯片串口发送数据状态输出引脚，任意串口有数据正在发送时，TX\_S/TX\_S2 引脚输出周期为 200mS 的脉冲电平。RX\_S/RX\_S2 为芯片串口接收数据状态输出引脚，任意串口有数据正在接收时，RX\_S/RX\_S2 引脚输出周期为 200mS 的脉冲电平。

CH9111 芯片的串口内置了独立的收发缓冲区，支持单工、半双工或者全双工异步串行通讯。

UART 的串行数据包括 1 个低电平起始位、5/6/7/8 个数据位、1 个/2 个高电平停止位，支持无校验/奇校验/偶校验/标志位/空白位。支持常用通讯波特率：1200、2400、3600、4800、9600、14400、19200、28800、38400、57600、76800、115200、128000、153600、230400、460800、921600、1M、1.5M、2M、2.5M、3M、4M、5M、6M、7.5M、10M、12M、15M 等。

CH9111 芯片的异步串口支持 CTS0 和 RTS0 硬件自动流控制，可以通过 CFG0 引脚配置启用或不启用（默认），也可以通过 VCP 厂商驱动程序进行独立配置。如果启用，那么仅在检测到 CTS0 引脚输入有效（低电平有效）时串口才继续发送下一包数据，否则暂停串口发送；当接收缓冲区空时，串口会自动有效 RTS0 引脚（低电平有效），直到接收缓冲区的数据较满时，串口才自动无效 RTS0 引脚，并在缓冲区空时再次有效 RTS0 引脚。使用硬件自动速率控制，可以将己方的 CTS0 引脚接到对方的 RTS0 引脚，并将己方的 RTS0 引脚送到对方的 CTS0 引脚。

CH9111 串口接收信号的允许波特率误差不大于 2%，串口发送信号的波特率误差小于 1.5%。

在计算机端的 Windows 操作系统下，CH9111 支持系统自带的 CDC 类驱动程序，也可安装高速率的 VCP 厂商驱动程序，能够仿真标准串口，所以绝大部分串口应用程序完全兼容，通常无需任何修改。在 VCP 厂商驱动程序模式下，支持最多 14 路 GPIO 输入输出控制功能。模式 0 支持最多 14 路 GPIO (GPIO0-13)，模式 1 支持最多 7 路 GPIO (GPIO0-6)。

CH9111 可以用于升级原串口外围设备，或者通过 USB 总线为计算机增加额外串口。通过外加电平转换器件，可以进一步提供 RS232、RS485、RS422 等接口。

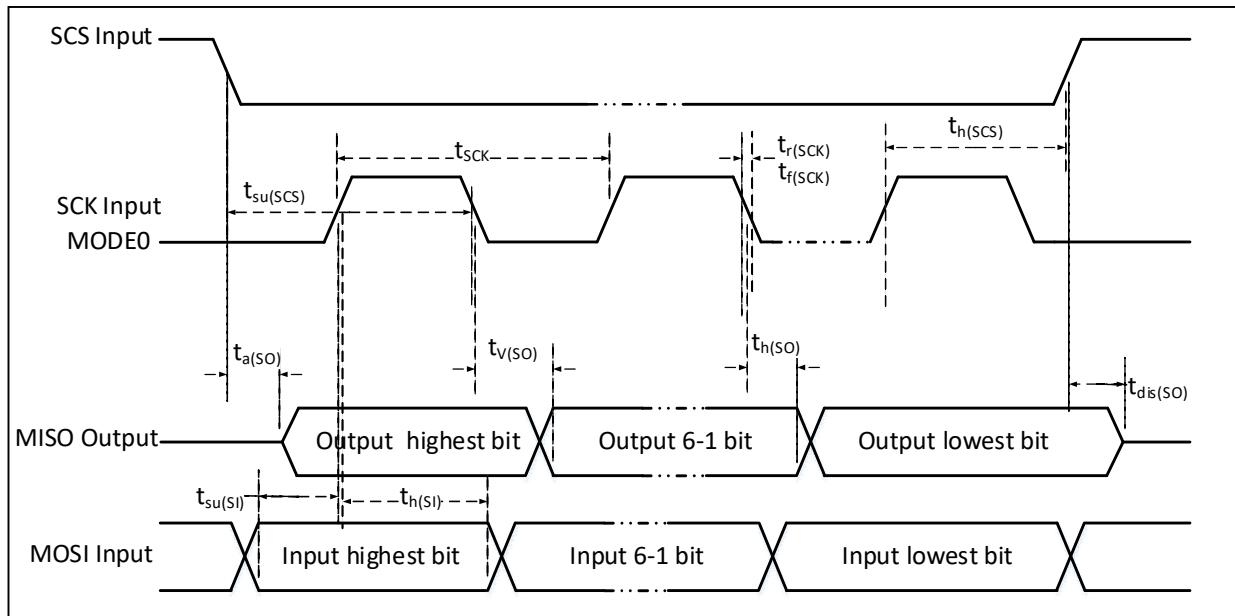

### 5.4 SPI 接口说明

CH9111L 芯片的 SPI 接口工作在从机模式，包括 4 根信号线 SCS、SCK、MISO、MOSI 和 3 根控制线 RDNE、WRNF、RWS。支持数据流控功能，RDNE 和 WRNF 是可选的。通过 SPI 接口，CH9111L 可以连接到各种 MCU、DSP 或 FPGA 等设备，实现 USB 虚拟串口和外部 SPI 主机的数据双向透传功能。CH9111L 接收外部 SPI 主机发送的数据并通过 USB 接口上传，同时接收 USB 接口下传的数据并通知外部 SPI 主机来读取，提供计算机端的 USB 高速驱动和 USB 转被动 SPI 接口函数库。

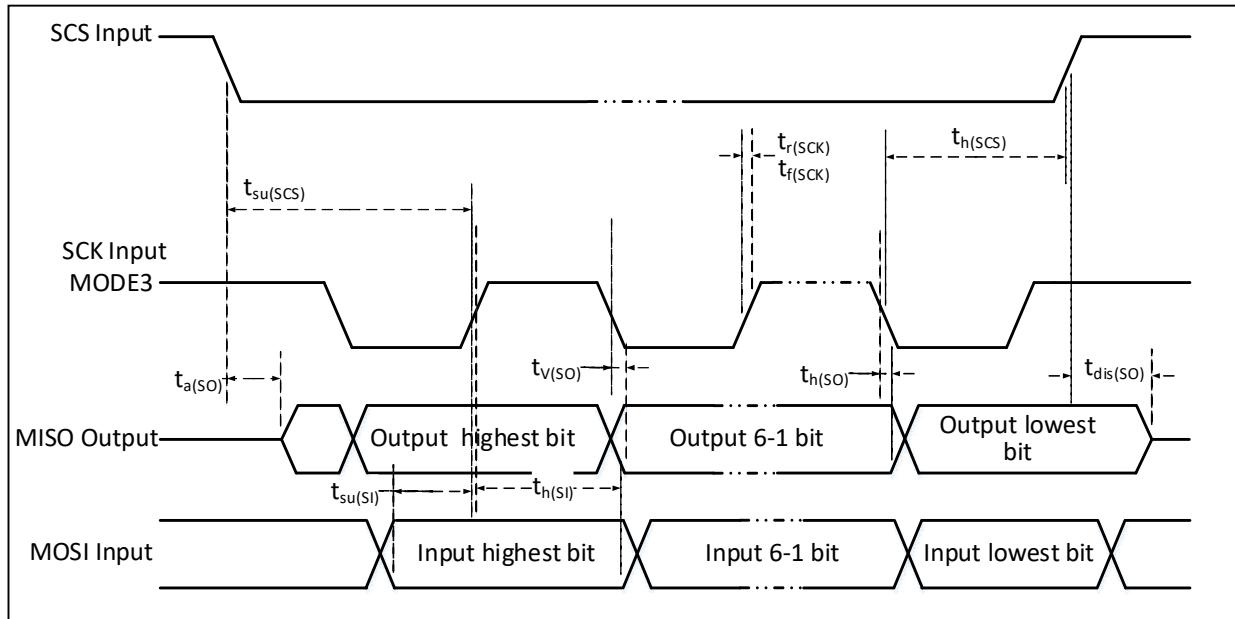

SPI 接口主机需要工作在模式 0 或模式 3。

SPI 接口主机向 CH9111L 芯片发送数据（写模式）流程：

步骤 1：SPI 接口主机控制 RWS 引脚输出高电平，通知 CH9111L 芯片需要切换为写模式；

步骤 2：检测 CH9111L 芯片的 WRNF 引脚状态，如果检测到低电平表示 CH9111L 芯片的接收 FIFO 还有空间可以接收一包（最大为 512 字节）数据，则执行步骤 3；如果检测到高电平表示 CH9111L 芯片的接收 FIFO 已满，则重新执行步骤 2；

步骤 3: SPI 接口主机执行数据发送操作, 向 CH9111L 芯片最多发送 512 字节数据, 并等待数据发送结束;

步骤 4: 如果 SPI 主机需要继续发送数据, 则重新执行步骤 2;

SPI 接口主机从 CH9111L 芯片读取数据(读模式)流程:

步骤 1: SPI 接口主机控制 RWS 引脚输出低电平, 通知 CH9111L 芯片需要切换为读模式, 等待 WRNF 引脚拉高或者等待至少 6us (仅从写模式切换到读模式时需要等待);

步骤 2: 检测 CH9111L 芯片的 RDNE 引脚状态, 如果检测到低电平表示 CH9111L 芯片的发送 FIFO 中有数据可以读取, 则执行步骤 3; 如果检测到高电平, 表示 CH9111L 芯片的发送 FIFO 无数据可以读取, 则重新执行步骤 2;

步骤 3: SPI 接口主机执行数据读取操作, 根据应用方式不同有以下 3 种进行读取方式:

方式 1: 拉低 SCS, 从 CH9111L 芯片读取 4 个字节的本包数据长度 L(低字节在前, 最大为 512 字节), 再根据实际长度读取 L 个字节的数据, 拉高 SCS;

方式 2: 拉低 SCS, 从 CH9111L 芯片读取 4 个字节的本包数据长度 L(低字节在前, 最大为 512 字节), 拉高 SCS; 再次拉低 SCS, 读取 4+L 个字节的数据, 拉高 SCS;

方式 3: 拉低 SCS, 从 CH9111L 芯片读取固定 516 个字节的数据, 前 4 个字节为本包数据长度, 后 512 字节为实际数据, 拉高 SCS;

步骤 4: 如果 SPI 主机需要继续读取, 重新执行步骤 2。

图 5-1 SPI 接口时序图 (MODE0)

图 5-2 SPI 接口时序图 (MODE3)

表 5-2 SPI 接口特性

| 名称                              | 参数说明          | 最小值 | 最大值 | 单位  |

|---------------------------------|---------------|-----|-----|-----|

| $f_{SCK}/t_{SCK}$               | SPI 时钟频率      |     | 40  | MHz |

| $t_r(SCK)^{(1)}/t_f(SCK)^{(1)}$ | SPI 时钟上升和下降时间 |     | 11  | ns  |

| $t_{SU(SCS)}$                   | SCS 建立时间      | 33  |     | ns  |

| $t_h(SCS)$                      | SCS 保持时间      | 33  |     | ns  |

| $t_{SU(SI)}$                    | 数据输入建立时间      | 4   |     | ns  |

| $t_h(SI)$                       | 数据输入保持时间      | 2   |     | ns  |

| $t_a(SO)$                       | 数据输出访问时间      | 0   | 17  | ns  |

| $t_{dis(SO)}$                   | 数据输出禁止时间      | 0   | 10  | ns  |

| $t_v(SO)$                       | 数据输出有效时间      |     | 15  | ns  |

| $t_h(SO)$                       | 数据输出保持时间      | 5   |     | ns  |

注 1: 负载电容:  $C=30pF$ 。

## 5.5 芯片参数配置

在较大批量应用时, CH9111 的厂商识别码 VID 和产品识别码 PID 以及产品信息可以定制。

在少量应用时, 可以使用内置的 EEPROM 进行参数配置。用户安装 VCP 厂商驱动程序后, 可以通过芯片厂家提供的配置软件 CH34xSerCfg.exe, 灵活配置芯片的厂商识别码 VID、产品识别码 PID、最大电流值、BCD 版本号、厂商信息和产品信息字符串描述符等参数。

## 6、参数

### 6.1 绝对最大值 (临界或者超过绝对最大值将可能导致芯片工作不正常甚至损坏)

| 名称            | 参数说明                 | 最小值  | 最大值 | 单位 |

|---------------|----------------------|------|-----|----|

| $T_A$         | 工作时的环境温度             | -40  | 85  | °C |

| $T_S$         | 储存时的环境温度             | -40  | 105 | °C |

| $V_{DD5}-GND$ | 工作电源电压 ( $V_{DD5}$ ) | -0.4 | 5.5 | V  |

|                 |                       |      |                |   |

|-----------------|-----------------------|------|----------------|---|

| $V_{DD33}$ -GND | 工作电源电压 ( $V_{DD33}$ ) | -0.4 | 4.0            | V |

| $V_{IO}$ -GND   | I/O 电源电压 ( $V_{IO}$ ) | -0.4 | 4.0            | V |

| $V_{USB}$       | USB 信号引脚上的电压          | -0.4 | $V_{DD33}+0.4$ | V |

| $V_{IO5V}$      | 耐受 5V 的 I/O 引脚上的电压    | -0.4 | 5.5            | V |

| $V_{UART}$      | 串口及其它引脚上的电压           | -0.4 | $V_{IO}+0.4$   | V |

## 6.2 电气参数 (测试条件: $T_A = 25^\circ C$ , $V_{DD33} = 3.3V$ , 不含 USB 引脚)

| 名称                | 参数说明                              | 最小值             | 典型值          | 最大值      | 单位        |

|-------------------|-----------------------------------|-----------------|--------------|----------|-----------|

| $V_{DD5}$         | 电源电压 ( $V_{DD5}$ 引脚供电, GND 引脚接地)  | 4.0             | 5.0          | 5.25     | V         |

| $V_{DD33}$        | 电源电压 ( $V_{DD33}$ 引脚供电, GND 引脚接地) | 3.0             | 3.3          | 3.6      | V         |

| $V_{IO}$          | I/O 引脚供电电压                        | 1.1             | 3.3          | 3.6      | V         |

| $I_{CC}$          | 芯片正常工作时的电源电流                      | 20              | 30           | 40       | mA        |

| $I_{SLP}$         | USB 挂起时的电源电流                      | 200             | 300          | 450      | uA        |

| $V_{IL}$          | 低电平输入电压                           | $V_{IO} = 3.3V$ | 0            | 0.8      | V         |

|                   |                                   | $V_{IO} = 1.8V$ | 0            | 0.6      | V         |

|                   |                                   | $V_{IO} = 1.2V$ | 0            | 0.4      | V         |

| $V_{IH}$          | 高电平输入电压                           | $V_{IO} = 3.3V$ | 2.2          | $V_{IO}$ | V         |

|                   |                                   | $V_{IO} = 1.8V$ | 1.2          | $V_{IO}$ | V         |

|                   |                                   | $V_{IO} = 1.2V$ | 0.8          | $V_{IO}$ | V         |

| $V_{IH5}$         | 耐受 5V 的引脚的高电平输入电压                 | $V_{IO} = 3.3V$ | 2.2          | 5        | V         |

|                   |                                   | $V_{IO} = 1.8V$ | 1.2          | 5        | V         |

|                   |                                   | $V_{IO} = 1.2V$ | 0.8          | 5        | V         |

| $V_{OL}$          | 输出低电压, 单个引脚吸入 5mA 电流              |                 | 0.4          | 0.6      | V         |

| $V_{OH}$          | 输出高电平, 单个引脚输出 5mA 电流              | $V_{IO}-0.6$    | $V_{IO}-0.4$ |          | V         |

| $R_{PU}$          | 内置上拉的等效电阻                         | 30              | 40           | 55       | $k\Omega$ |

| $V_{POR}/V_{PDR}$ | $V_{DD33}$ 上电/掉电复位的阈值电压           | 2.55            | 2.7          | 2.85     | V         |

| $V_{ESD}$         | ESD 静电耐受电压<br>(HBM 人体模型, 非接触式)    |                 | 6            |          | kV        |

## 6.3 时序参数 (测试条件: $T_A = 25^\circ C$ , $V_{DD33} = 3.3V$ )

| 名称         | 参数说明                 | 最小值                                 | 典型值  | 最大值 | 单位      |

|------------|----------------------|-------------------------------------|------|-----|---------|

| FD         | 内部时钟的误差<br>(同比影响波特率) | $T_A = 0^\circ C \sim 70^\circ C$   | -1.2 |     | %       |

|            |                      | $T_A = -40^\circ C \sim 85^\circ C$ | -2.2 |     | %       |

| $T_{RSTD}$ | 电源上电或外部复位输入后的复位延时    |                                     | 15   | 30  | $\mu s$ |

| $T_{SUSP}$ | 检测 USB 自动挂起时间        |                                     | 3    | 5   | $\mu s$ |

| $T_{WAKE}$ | 芯片睡眠后唤醒完成时间          |                                     | 0.3  | 0.5 | $\mu s$ |

## 7、封装

说明：尺寸标注的单位是 mm（毫米）。

引脚中心间距是标称值，没有误差，除此之外的尺寸误差不大于±0.2mm。

### 7.1 LQFP48 封装

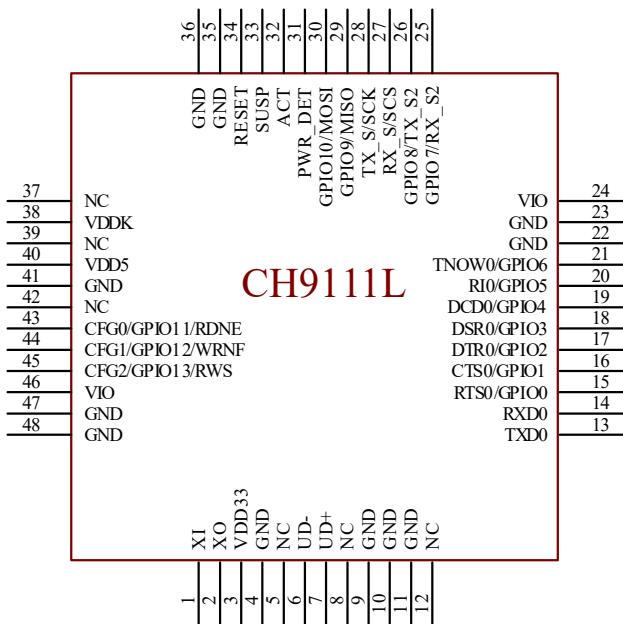

## 8、应用

### 8.1 USB 转 UART 串口+SPI 接口

下图 8-1 是由 CH9111 芯片实现的高速 USB 转 UART 串口+SPI 接口的参考电路图。图中的串口信号线可以只连接 RXD0、TXD0 以及公共地线，其它信号线 CTS0、RTS0、DTR0、DSR0、R10、DCD0 和 TNOW0 根据需要选用，不需要时都可以悬空。

P1 是 USB 端口，USB 总线包括一对 5V 电源线和一对数据信号线，通常，+5V 电源线是红色，接地线是黑色，D+信号线是绿色，D-信号线是白色。USB 总线提供的电源电流可以达到 500mA。

P2 为串口的 TTL 连接引脚，包括 GND、RXD0、TXD0、RTS0、CTS0、DTR0、DSR0、R10、DCD0 和 TNOW0 等引脚。可以外加电平转换器件，实现 TTL 转 RS232、RS485、RS422 等信号转换。

P3 为 SPI 接口连接引脚，包括 5V、3V3、GND、SCS、SCK、MISO、MOSI 和辅助引脚 RDNE、WRNF、RWS 引脚。

CH9111 芯片支持 5V 或 3.3V 电源电压，每个电源引脚应外接电源退耦电容，如图中 C7、C8、C9、C10、C11 和 C12 即为电源退耦电容。电源电压为 5V 时，建议增加 TVS 等过压保护器件。

JP3 为芯片工作电源选择跳线，芯片需要工作在 5V 时，短接第 5 脚和第 6 脚，无需 U1 芯片；芯片需要工作在 3.3V 时，短接第 1 脚和第 2 脚，短接第 3 脚和第 5 脚。

建议为 USB 信号线增加 ESD 保护器件，ESD 芯片寄生电容需小于 2pF，例如 CH412K，其 VDD33 应接 3.3V。

建议串口外设与 CH9111 芯片的 VIO 使用同一电源。

在设计印刷线路板 PCB 时，需要注意：退耦电容 C7、C8、C9、C10、C11 和 C12 尽量靠近 CH9111 相连的电源引脚；USB 口的 D+和 D-信号线按高速 USB 规范贴近平行布线，保证特性阻抗，尽量在两侧提供地线或者覆铜，减少来自外界的信号干扰。

图 8-1 高速 USB 转 UART 串口+SPI 接口参考电路图