## **SLC NAND Flash Memory Products Roadmap**

Memory Application Engineering Dept.2 Memory Division January, 2021

© 2021 KIOXIA Corporation. All Rights Reserved.

## **Overview**

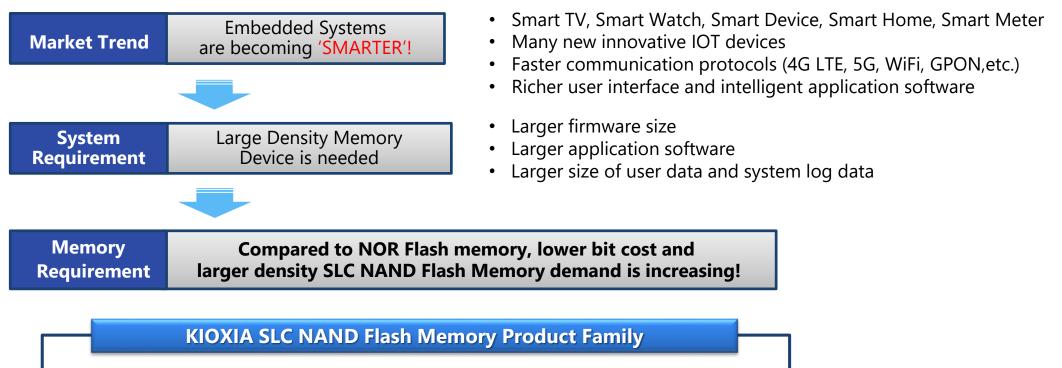

### **Demand for SLC NAND Flash Memory**

• BENAND<sup>™</sup>: Built-in ECC NAND

• All other company names, product names, and service names mentioned herein may be trademarks of their respective companies.

### **SLC NAND Flash Memory Product Concept**

\* The ECC logic in Serial Interface NAND can be enabled and disabled by the customers.

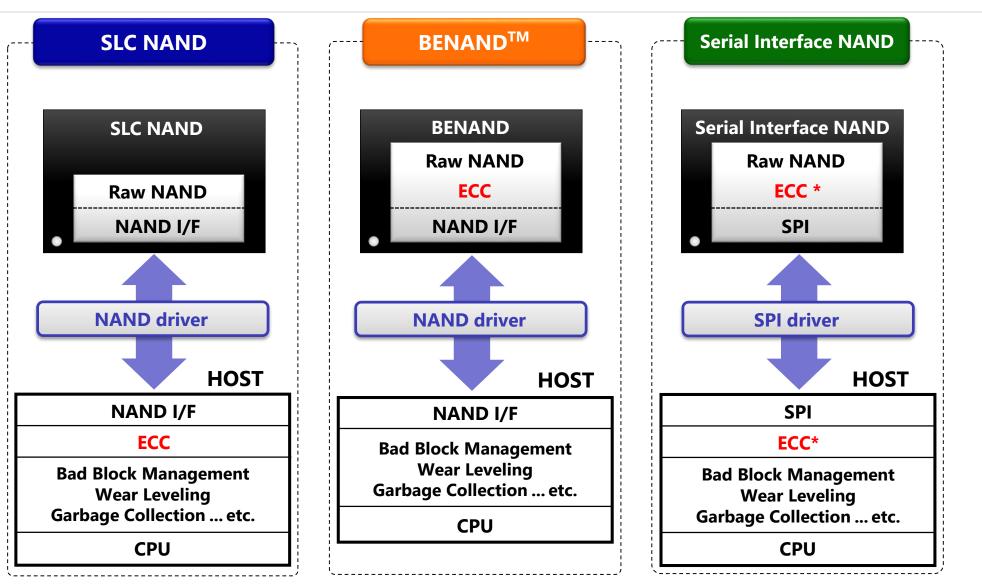

### KIOXIA NAND targets wide range of embedded applications. These applications are examples of target for SLC NAND product family.

KIOXIA

### KIOXIA will provide long-term support for SLC products and would like to grow our business with customers

| Process | s Capacity |    | ess Capacity |    |    | CY2021 |    | CY2022 |    | CY2023 |    | CY2024 |    | CY2025 |    |    |    |    |    |    |    |    |    |    |    |

|---------|------------|----|--------------|----|----|--------|----|--------|----|--------|----|--------|----|--------|----|----|----|----|----|----|----|----|----|----|----|

|         |            | 1Q | 2Q           | 3Q | 4Q | 1Q     | 2Q | 3Q     | 4Q | 1Q     | 2Q | 3Q     | 4Q | 1Q     | 2Q | 3Q | 4Q | 1Q | 2Q | 3Q | 4Q | 1Q | 2Q | 3Q | 4Q |

| 32nm    | 4-128Gb    |    |              |    |    |        |    |        |    |        |    |        |    |        |    |    |    |    |    |    |    |    |    |    |    |

| 24nm    | 1-256Gb    |    |              |    |    |        |    |        |    |        |    |        |    |        |    |    |    |    |    |    |    |    |    |    |    |

Notice:

- This roadmap is subject to change without notice.

- Broken lines in 32nm process depend on business conditions.

- 24nm SLC NAND includes BENAND and Serial Interface NAND.

### **SLC NAND Flash Memory Product Lineup**

### 24nm SLC NAND Product Lineup

| Density | SLC NAND      | BENAND™       | Serial Interface<br>NAND |

|---------|---------------|---------------|--------------------------|

| 256Gb   | 32Gb × 8 *    |               |                          |

| 128Gb   | 32Gb × 4      |               |                          |

| 64Gb    | 32Gb × 2      |               |                          |

| 32Gb    | 32Gb          |               |                          |

| 16Gb    | 4Gb × 4       |               |                          |

| 8Gb     | 4Gb × 2       | 4Gb × 2       | 4Gb x 2                  |

| 4Gb     | 4Gb / 2Gb × 2 | 4Gb / 2Gb × 2 | 4Gb                      |

| 2Gb     | 2Gb           | 2Gb           | 2Gb                      |

| 1Gb     | 1Gb           | 1Gb           | 1Gb                      |

\* 256Gbit SLC NAND product is only available on Toggle I/F.

✓ Offers wide lineup of density and package type

Adopted in a wide range of applications from consumer use to industrial use because of its high Read / Write speed and high reliability

✓ BENAND<sup>™</sup> with built-in ECC in SLC NAND and Serial Interface NAND with interface of Serial Peripheral Interface are available

### ΚΙΟΧΙΑ

## SLC NAND Flash Memory (Raw SLC NAND)

### **SLC NAND**

To meet needs of diverse customers' application, our SLC NAND flash memory products offer wide line-up of density and package type.

SLC NAND is adopted in a wide range of applications from consumer use to industrial use because of its high Read and Write speed and high reliability.

- Features of SLC NAND

- ✓ 24nm SLC NAND process technology

- ✓ Available diverse package lineup for customer's needs 48TSOP (12 x 20 mm) / 63BGA (9 x 11 mm) / 67BGA (6.5 x 8 mm)

- Offers wide lineup of density

1Gbit, 2Gbit, 4Gbit, 8Gbit and 16Gbit are available in a lineup

- \* Please contact the KIOXIA sales representative for information about 32Gb die products.

### **SLC NAND Roadmap (1Gbit - 4Gbit)**

| Density | Page/<br>Block<br>Size | Process | CY2020            | CY2021 | CY2022<br>1Q 2Q 3Q 4Q | CY2023<br>1Q 2Q 3Q 4Q | CY2024<br>1Q 2Q 3Q 4Q | CY2025 |

|---------|------------------------|---------|-------------------|--------|-----------------------|-----------------------|-----------------------|--------|

| 1Gbit   |                        | 24nm    | 1Gb x 1Chip       |        |                       |                       |                       |        |

| 2Gbit   | 2KB/<br>128KB          | 24nm    | 2Gb x 1Chip       |        |                       |                       |                       |        |

|         |                        | 24nm    | 2Gb x 2Chips (1Cl | E)     |                       |                       |                       |        |

| 4Gbit   | 4KB/                   | 32nm    |                   |        |                       |                       |                       |        |

|         | 256KB                  | 24nm    | 4Gb x 1Chip       |        |                       |                       |                       |        |

Notice:

- This roadmap is subject to change without notice.

### SLC NAND Roadmap (8Gbit - 32Gbit)

| Density | Page/<br>Block<br>Size | Process | CY2020          | CY2021      | CY2022      | CY2023      | CY2024      | CY2025      |

|---------|------------------------|---------|-----------------|-------------|-------------|-------------|-------------|-------------|

|         |                        |         | 1Q 2Q 3Q 4Q     | 1Q 2Q 3Q 4Q | 1Q 2Q 3Q 4Q | 1Q 2Q 3Q 4Q | 1Q 2Q 3Q 4Q | 1Q 2Q 3Q 4Q |

| 8Gbit   |                        | 32nm    |                 |             |             |             |             |             |

| odbit   |                        | 24nm    | 4Gb x 2Chips (1 | CE)         |             |             |             |             |

| 16Gbit  | 4KB/<br>256KB          | 32nm    |                 |             |             |             |             |             |

| rodbit  |                        | 24nm    | 4Gb x 4Chips (2 | CE)         |             |             |             |             |

| 32Gbit  |                        | 32nm    |                 |             |             |             |             |             |

#### Notice:

- This roadmap is subject to change without notice.

- Broken lines in 32nm process depend on business conditions.

### SLC NAND Roadmap (32Gb die products: 32Gbit - 256Gbit)

| Density | Page/<br>Block | Process | CY2020        | CY2021      | CY2022      | CY2023      | CY2024      | CY2025      |

|---------|----------------|---------|---------------|-------------|-------------|-------------|-------------|-------------|

|         | Size           |         | 1Q 2Q 3Q 4Q   | 1Q 2Q 3Q 4Q | 1Q 2Q 3Q 4Q | 1Q 2Q 3Q 4Q | 1Q 2Q 3Q 4Q | 1Q 2Q 3Q 4Q |

| 32Gbit  |                | 24nm    | 32Gb x 1chip  |             |             |             |             |             |

| 64Gbit  | 8KB/           | 24nm    | 32Gb x 2chips |             |             |             |             |             |

| 128Gbit | 1MB            | 24nm    | 32Gb x 4chips |             |             |             |             |             |

| 256Gbit |                | 24nm    | 32Gb x 8chips |             |             |             |             |             |

#### Notice:

- This roadmap is subject to change without notice.

- 24nm 32Gbit die base products are Vcc=3.3V only.

- Requires ECC 24bits/1KB correction and data randomization for 24nm 32Gbit die based products.

#### Interface Lineup

| Density | Inter        | Interface    |  |  |  |  |  |

|---------|--------------|--------------|--|--|--|--|--|

| Density | Legacy       | Toggle 2.0   |  |  |  |  |  |

| 32Gbit  | $\checkmark$ | -            |  |  |  |  |  |

| 64Gbit  | $\checkmark$ | $\checkmark$ |  |  |  |  |  |

| 128Gbit | $\checkmark$ | $\checkmark$ |  |  |  |  |  |

| 256Gbit | -            | $\checkmark$ |  |  |  |  |  |

### KIOXIA

#### SUBJECT TO CHANGE WITHOUT NOTICE <For Recipient Eyes Only>

M2PLZ00-1026

January, 2021 Confidential

### **1Gbit / 2Gbit SLC NAND Specification**

| S                  | SLC NAND Die Density             | 1G           | bit          | 2G           | bit          |  |

|--------------------|----------------------------------|--------------|--------------|--------------|--------------|--|

|                    | NAND Design Rule                 | 24r          | ۱m           | 241          | nm           |  |

| ECC Requirement    |                                  | 8bit/5       | 12Byte       | 8bit/5       | 12Byte       |  |

|                    | Power Supply                     |              | 3.3V 1.8V    |              | 1.8V         |  |

|                    | Page Size [Bytes]                | 2048         | +128         | 2048         | +128         |  |

| Architecture       | Pages Per Block                  | 64           | 4            | 6            | 4            |  |

| Architecture       | Block Size [Bytes]               | 128K         | (+8K         | 128k         | (+8K         |  |

|                    | Valid Blocks                     | 1004 -       | 1024         | 2008 - 2048  |              |  |

|                    | Plane                            | 1            |              | 2            | 2            |  |

| Operation          | Cache Operation                  | Sup          | oort         | Sup          | port         |  |

| Operation          | Multi Page/Block Operation       | Not Su       | ipport       | Sup          | port         |  |

|                    | tWC & tRC (Max. Data Rate)       | 25           | ns           | 25ns         |              |  |

| Dorformanco        | tPROG (typ.)                     | 300          | )μs          | 300µs        |              |  |

| Performance        | Performance tR (max)             |              | μs           | 25           | μs           |  |

| tBERASE (typ.)     |                                  | 2.5ms        | 3.5ms        | 2.5ms        | 3.5ms        |  |

|                    | TSOP48 (0 to 70°C / -40 to 85°C) | ✓            | -            | $\checkmark$ | -            |  |

| Package<br>(Temp.) | FBGA63 (-40 to 85°C)             | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

|                    | FBGA67 (-40 to 85°C)             | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

### **4Gbit / 8Gbit SLC NAND Specification**

| S                  | LC NAND Die Density              |              | 4G           | bit          |              | 8G           | bit          |

|--------------------|----------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|

|                    | NAND Design Rule                 | 32ı          | nm           | 24r          | าฑ           | 32           | nm           |

|                    | ECC Requirement                  |              | 12Byte       | 8bit/5       | 12Byte       | 4bit/512Byte |              |

|                    | Power Supply                     | 3.3V         | 1.8V         | 3.3V         | 1.8V         | 3.3V         | 1.8V         |

|                    | Page Size [Bytes]                | 4096         | +224         | 4096         | +256         | 4096         | +232         |

| Architactura       | Pages Per Block                  | 6            | 4            | 6            | 4            | 6            | 4            |

| Architecture       | Block Size [Bytes]               | 256K         | +14K         | 256K         | +16K         | 256K+        | -14.5K       |

|                    | Valid Blocks                     | 2008 -       | - 2048       | 2008 - 2048  |              | 4016 - 4096  |              |

|                    | Plane                            |              | 2            | 2            | <u>)</u>     | 2            |              |

| Operation          | Cache Operation                  | Support      |              | Sup          | oort         | Sup          | port         |

| Operation          | Multi Page/Block Operation       | Sup          | port         | Support      |              | Support      |              |

|                    | tWC & tRC (Max. Data Rate)       | 25           | ins          | 25ns         |              | 25ns         |              |

| Dorformonco        | tPROG (typ.)                     | 300          | Ͻμs          | 300µs        |              | 300µs        |              |

| Performance        | tR (max)                         | 30           | lμs          | 25           | μs           | 30µs         |              |

| tBERASE (typ.)     |                                  | 3r           | ns           | 2.5ms        | 3.5ms        | 3r           | ns           |

|                    | TSOP48 (0 to 70°C / -40 to 85°C) | $\checkmark$ | -            | $\checkmark$ | -            | $\checkmark$ | -            |

| Package<br>(Temp.) | FBGA63 (-40 to 85°C)             | ✓            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| (1011)             | FBGA67 (-40 to 85°C)             | -            | -            | $\checkmark$ | $\checkmark$ | -            | -            |

### **32Gbit die SLC NAND Specification**

| S              | SLC NAND Die Density       | 320                                 | Gbit                                |

|----------------|----------------------------|-------------------------------------|-------------------------------------|

|                | NAND Design Rule           | 24                                  | nm                                  |

|                | Interface                  | Legacy                              | Toggle 2.0                          |

|                | ECC Requirement            | 24bit/1KByte                        | 24bit/1KByte                        |

|                | Power Supply               | 3.3V                                | 3.3V *                              |

|                | Page Size [Bytes]          | 8K+1K                               | 8K+1K                               |

| Architactura   | Pages Per Block            | 128                                 | 128                                 |

| Architecture   | Block Size [Bytes]         | 1M+128K                             | 1M+128K                             |

|                | Valid Blocks               | 4036 - 4156                         | 4036 - 4156                         |

|                | Plane                      | 2                                   | 2                                   |

| Operation      | Cache Operation            | Support                             | Support                             |

| Operation      | Multi Page/Block Operation | Support                             | Support                             |

|                | tWC & tRC (Max. Data Rate) | 20ns                                | 400MT/s                             |

|                | tPROG (typ.)               | 400µs                               | 400µs                               |

| Performance    | tR (typ./ max)             | 35µs/45µs                           | 35µs/45µs                           |

| tBERASE (typ.) |                            | 4.5ms                               | 4.5ms                               |

|                | Package (Temp.)            | TSOP48<br>(0 to 70°C / -40 to 85°C) | BGA132<br>(0 to 70°C / -40 to 85°C) |

VccQ and Vcc may be distinct and unique voltages on Toggle I/F product. The device shall support one of the following VccQ/Vcc combinations,

/cc = 3.3V, VccQ = 3.3V /cc = 3.3V, VccQ = 1.8V

3.3V VccQ is not supported for the case where transfer rate is greater than 100MHz.

✓ Required data randomization for 24nm 32Gbit die based products.

## BENAND<sup>TM</sup> (Built-in ECC NAND)

BENAND (Built-in ECC NAND) is a SLC NAND memory device which has an Internal Hardware ECC Engine.

Using BENAND it is possible for customers to use 24nm SLC NAND flash memory technology even when their platform cannot support higher bit ECC.

- Features of BENAND

- ✓ Embedded ECC engine

Provides information of ECC correction, ECC on Host controller is not required

- ✓ 24nm SLC NAND process technology

- Offers wide line-up of density

1Gbit, 2Gbit, 4Gbit, and 8Gbit are available in a lineup

- Compatibility of SLC NAND Interface, basic functions and command sequence follows SLC NAND

| Density | Page/<br>Block<br>Size | Process | CY2020<br>1Q 2Q 3Q 4Q | CY2021<br>1Q 2Q 3Q 4Q | CY2022<br>1Q 2Q 3Q 4Q | CY2023<br>1Q 2Q 3Q 4Q | CY2024<br>1Q 2Q 3Q 4Q | CY2025<br>1Q 2Q 3Q 4Q |

|---------|------------------------|---------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 1Gbit   | ,                      | 24nm    | 1Gb x 1Chip           |                       |                       |                       |                       |                       |

| 2Gbit   | 2KB/<br>128KB          | 24nm    | 2Gb x 1Chip           |                       |                       |                       |                       |                       |

|         |                        | 24nm    | 2Gb x 2Chips (        | ICE)                  |                       |                       |                       |                       |

| 4Gbit   | 4KB/                   | 24nm    | 4Gb x 1Chip           |                       |                       |                       |                       |                       |

| 8Gbit   | 256KB                  | 24nm    | 4Gb x 2Chips (        | 1 <u>CE</u> )         |                       |                       |                       |                       |

Notice:

- This roadmap is subject to change without notice.

Process 24nm

### KIOXIA

### 1/2/4Gbit BENAND Specification

| [                  | BENAND Die Density               | 1G           | bit          | 2G           | bit          | <b>4</b> G   | bit          |  |

|--------------------|----------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--|

|                    | NAND Design Rule                 | 241          | nm           | <u> </u> 24ı | าฑ           | 24           | nm           |  |

|                    | ECC Requirement                  |              | quired       | Not Re       | quired       | Not Required |              |  |

|                    | Power Supply                     | 3.3V         | 1.8V         | 3.3V         | 1.8V         | 3.3V         | 1.8V         |  |

|                    | Page Size [Bytes]                | 2048         | 3+64         | 2048         | 8+64         | 4096         | +128         |  |

| Architactura       | Pages Per Block                  | 6            | 4            | 6            | 4            | 6            | 4            |  |

| Architecture       | Block Size [Bytes]               | 128k         | (+4K         | 128k         | K+4Κ         | 256          | K+8K         |  |

|                    | Valid Blocks                     | 1004 -       | - 1024       | 2008 -       | 2048         | 2008 - 2048  |              |  |

|                    | Plane                            | -            | 1            | 2            |              |              | 2            |  |

| Operation          | Cache Operation                  | Not Su       | upport       | Not Su       | ipport       | Not Si       | upport       |  |

| Operation          | Multi Page/Block Operation       | Not Su       | upport       | Support      |              | Support      |              |  |

|                    | tWC & tRC (Max Data Rate)        | 25           | ns           | 25ns         |              | 25ns         |              |  |

| Performance        | tPROG (typ.)                     | 330µs        |              | 330          | 330µs        |              | Ͻμs          |  |

| Periormance        | tR (typ./max)                    | 40µs /       | 120µs        | 40µs /       | 120µs        | 55µs / 220µs |              |  |

|                    | tBERASE (typ.)                   |              | 3.5ms        | 2.5ms        | 3.5ms        | 2.5ms        | 3.5ms        |  |

| Destaura           | TSOP48 (0 to 70°C / -40 to 85°C) | $\checkmark$ | -            | $\checkmark$ | -            | $\checkmark$ | -            |  |

| Package<br>(Temp.) | FBGA63 (-40 to 85°C)             | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| (remp.)-           | FBGA67 (-40 to 85°C)             | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

✓ tR and tPROG of AC timing parameters for BENAND includes the internal ECC operation time.

✓ For more information, please refer to datasheet of respective product.

### ΚΙΟΧΙΑ

## **Serial Interface NAND**

Serial Interface NAND is a SLC NAND memory device with Serial Peripheral Interface (SPI). SPI is one of the most common interfaces in SoC today and is offered in small package size.

- Features of Serial Interface NAND

- Host can control the device by a low pin count

Supports Mode 0 and Mode 3 of Serial Peripheral Interface (SPI)

- Embedded ECC engine Provides information of ECC correction, ECC on Host controller is not required

- ✓ 24nm SLC NAND process technology

- ✓ Offers wide line-up of density

1Gbit, 2Gbit, 4Gbit and 8Gb are available in a lineup

- ✓ Available in small package 6 x 8mm WSON8

\* The ECC function in Serial Interface NAND can be enabled and disabled by the customers.

WSON Package

### Uplifting the application with KIOXIA's Serial NAND

### ■ Lineup

| NAND Generation | : 24nm            |

|-----------------|-------------------|

| Density         | : 1 / 2 / 4 / 8Gb |

| Package         | : WSON8           |

| Vcc             | : 3.3V / 1.8V     |

| Operation Temp. | : -40 to 85 deg.  |

### Feature

Max. CLK Frequency: 133MHzInterface: SPI (x1, x2, x4) Mode 0, Mode 3ECC \*: 8bit ECC for each 528Byte is implemented.

\* The ECC function in Serial Interface NAND can be enabled and disabled by the customers.

| Density | Page/<br>Block Size | Process | CY2020       | CY2021 | CY2022<br>1Q 2Q 3Q 4Q | CY2023<br>1Q 2Q 3Q 4Q | CY2024 | CY2025 |

|---------|---------------------|---------|--------------|--------|-----------------------|-----------------------|--------|--------|

| 1Gbit   | 2KB/                | 24nm    |              |        |                       |                       |        |        |

| 2Gbit   | 128KB               |         |              |        |                       |                       |        |        |

| 4Gbit   | 4KB/<br>256KB       | 24nm    |              |        |                       |                       |        |        |

| 8Gbit   | 4KB/<br>256KB       | 24nm    | 4Gb x 2Chips |        |                       |                       |        |        |

Notice:

- This roadmap is subject to change without notice.

1st generation

2nd generation

#### ΚΙΟΧΙΑ

### **Serial Interface NAND Specification (2nd Generation)**

| Density               |                          |                  | 1Gbit                                               |       | 2Gbit       |       | 4Gbit       |       | 8Gbit       |       |

|-----------------------|--------------------------|------------------|-----------------------------------------------------|-------|-------------|-------|-------------|-------|-------------|-------|

| NAND Design Rule      |                          |                  | 24nm                                                |       | 24nm        |       | 24nm        |       | 24nm        |       |

| I/F Specification     |                          |                  | SPI (x1, x2, x4) Mode 0, Mode 3                     |       |             |       |             |       |             |       |

| ECC Requirement       |                          |                  | 8bit ECC for each 528Byte is implemented.           |       |             |       |             |       |             |       |

|                       | Power Supply             |                  | 3.3V                                                | 1.8V  | 3.3V        | 1.8V  | 3.3V        | 1.8V  | 3.3V        | 1.8V  |

|                       | Page Size                | Internal ECC On  | 2048+64                                             |       | 2048+64     |       | 4096+128    |       | 4096+128    |       |

|                       | [Bytes]                  | Internal ECC Off | 2048+128                                            |       | 2048+128    |       | 4096+256    |       | 4096+256    |       |

| Architecture          | Pages Per Block          |                  | 64                                                  |       | 64          |       | 64          |       | 64          |       |

|                       | Block Size<br>[Bytes]    | Internal ECC On  | 128K+4K                                             |       | 128K+4K     |       | 256K+8K     |       | 256K+8K     |       |

|                       |                          | Internal ECC Off | 128K+8K                                             |       | 128K+8K     |       | 256K+16K    |       | 256K+16K    |       |

|                       | Valid Blocks             |                  | 1004 - 1024                                         |       | 2008 - 2048 |       | 2008 - 2048 |       | 4016 - 4096 |       |

|                       | Data Transfer Rate (max) |                  | 133MHz                                              |       | 133MHz      |       | 133MHz      |       | 133MHz      |       |

| Deufeureere           | tPROG (typ.)             |                  | 360µs                                               |       | 360µs       |       | 450µs       |       | 450µs       |       |

| Performance           | tR (typ.)                |                  | 70µs                                                |       | 70µs        |       | 115µs       |       | 115µs       |       |

|                       | tBERASE (typ.)           |                  | 2.0ms                                               | 2.7ms | 2.0ms       | 2.7ms | 2.0ms       | 2.7ms | 2.0ms       | 2.7ms |

| Special Function      |                          |                  | Block Protection(OTP),<br>ECC Bit Flip Count Report |       |             |       |             |       |             |       |

| Package & Temperature |                          |                  | WSON8<br>-40 to 85°C                                |       |             |       |             |       |             |       |

Notice:

- This specification is tentative and subject to change without notice.

### ΚΙΟΧΙΑ

## **Package Information**

### 24nm SLC NAND/ BENAND Package

| Туре                                      |                                                                                                                                                                                                                                                                                        |              | FBG                                                                                         | A63          | TSOF                                                                                                                                                                                                        | 248                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Size<br>Vcc<br>Temp.<br>Pin/Ball<br>Pitch | 6.5 x 8mm<br>3.3V&1.8V<br>-40 to 85°C<br>67Balls<br>0.8mm                                                                                                                                                                                                                              |              | 9 x 11mm<br>3.3V&1.8V<br>-40 to 85°C<br>63Balls<br>0.8mm                                    |              | 12 x 20mm<br>3.3V<br>0 to 70°C / -40 to 85°C<br>48Pins<br>0.5mm                                                                                                                                             | TC58NVG2S0HTA00                                                                                                                                                                                                                                                                                                                                        |

| Pin Assignment<br>(Top View)              | ○ NC NC NC NC NC NC<br>NC WP ALE Vss CE WE R/B NC<br>NC NC RE CLE NC NC NC NC<br>NC NC RE CLE NC NC NC NC<br>NC NC NC NC NC NC NC<br>NC V02 NC Vcc)/06//08 NC<br>NC Vss //03//04//03//07 Vss NC<br>NC NC NC NC NC NC NC |              | NC NC<br>NC NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>N |              | NC = 1<br>NC = 2<br>NC = 3<br>NC = 4<br>NC = 6<br>RY/BY = 7<br>RE = 8<br>CE = 9<br>NC = 10<br>NC = 11<br>Vcc = 12<br>Vss = 13<br>NC = 14<br>NC = 16<br>ALE = 17<br>WE = 18<br>WP = 19<br>NC = 22<br>NC = 24 | 48 D NC<br>47 D NC<br>46 D NC<br>45 D NC<br>44 D I/O8<br>43 D I/O7<br>42 D I/O6<br>41 D I/O5<br>40 D NC<br>39 D NC<br>38 D NC<br>37 D V <sub>SS</sub><br>35 D NC<br>33 D NC<br>32 D I/O4<br>31 D I/O2<br>29 D I/O1<br>28 D NC<br>27 D NC<br>26 D NC<br>25 D NC |

| Lineup                                    | SLC NAND                                                                                                                                                                                                                                                                               | BENAND       | SLC NAND                                                                                    | BENAND       | SLC NAND                                                                                                                                                                                                    | BENAND                                                                                                                                                                                                                                                                                                                                                 |

| 1Gbit                                     | $\checkmark$                                                                                                                                                                                                                                                                           | $\checkmark$ | $\checkmark$                                                                                | $\checkmark$ | $\checkmark$                                                                                                                                                                                                | $\checkmark$                                                                                                                                                                                                                                                                                                                                           |

| 2Gbit                                     | $\checkmark$                                                                                                                                                                                                                                                                           | $\checkmark$ | $\checkmark$                                                                                | $\checkmark$ | $\checkmark$                                                                                                                                                                                                | $\checkmark$                                                                                                                                                                                                                                                                                                                                           |

| 4Gbit                                     | $\checkmark$                                                                                                                                                                                                                                                                           | $\checkmark$ | $\checkmark$                                                                                | $\checkmark$ | $\checkmark$                                                                                                                                                                                                | $\checkmark$                                                                                                                                                                                                                                                                                                                                           |

| 8Gbit                                     | $\checkmark$                                                                                                                                                                                                                                                                           | $\checkmark$ | $\checkmark$                                                                                | $\checkmark$ | $\checkmark$                                                                                                                                                                                                | $\checkmark$                                                                                                                                                                                                                                                                                                                                           |

| 16Gbit                                    | -                                                                                                                                                                                                                                                                                      | -            | -                                                                                           | -            | $\checkmark$                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                      |

| 32Gbit                                    | -                                                                                                                                                                                                                                                                                      | -            | -                                                                                           | -            | ✓ (Legacy I/F)                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                      |

| 64Gbit                                    | -                                                                                                                                                                                                                                                                                      | -            | -                                                                                           | -            | ✓ (Legacy I/F)                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                      |

| 128Gbit                                   | -                                                                                                                                                                                                                                                                                      | -            | -                                                                                           | -            | ✓ (Legacy I/F)                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                      |

#### ΚΙΟΧΙΑ

### 24nm 32Gb die SLC NAND Package (Toggle I/F)

| Туре                         | BGA1                                                                                                                                                                                                                                                                                                                                                                 | 32                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Size                         | 12 x 18mm                                                                                                                                                                                                                                                                                                                                                            | 00000 00000                                                                                                                                                                                                                                                                                                                                                                       |

| Vcc                          | 3.3V *                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                   |

| Temp.                        | 0 to 70°C / -40 to 85°C                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                   |

| Ball                         | 132Balls                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                   |

| Pitch                        | 1.0mm                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                   |

| Pin Assignment<br>(Top View) | C NC NC<br>NC NC NC<br>NC NC NC<br>NU NU NU<br>NU VccQ VccQQ31 Vss<br>NU VssQ 022 VssQa51<br>(001)011003 RE-1<br>VssQ VccQ NLE-1CLE-1<br>NU NU WP1 NU<br>VssQ VccQ NLL-1CLE-1<br>NU NU WP1 NU<br>VssQ VccQ NU<br>NU NU CE0 NU<br>NU VssQ 023 VssQ RE1<br>NU VssQ 023 VccQ NU<br>NU<br>NU NU CE0 NU<br>NU NU CE0 VccQ NU<br>NU VssQ 023 VccQ NU<br>NU<br>NU NU CE0 NU | NC NC NC<br>NC NC NC<br>NC NC NC<br>NU NU NU<br>Vec Q4-1/vccQ/vccQ NU<br>RE-1/vssQ0c5-1/vssQ NU<br>WE/REF DQ6-1/vssQ<br>NU CEI NU NU<br>NU RB Vec Vss<br>NU RB Vec Vss<br>NU RB Vec Vss<br>NU RB Vec Vss<br>NU RB Vec Qss<br>NU RD NU NU<br>CLE d/LE 0/vccQ/vssQ<br>RE-0 DQ5-0 dq1-0 dq0-0<br>q3-0 vssQ 0q2-0 vssQ NU<br>Vss Qq2-0 vssQ NU<br>NU NU NU NU<br>NC NC NC<br>NC NC NC |

| Lineup                       | SLC NA                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                   |

| 64Gbit                       | ✓ (Toggle                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                   |

| 128Gbit                      | ✓ (Toggle                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                   |

| 256Gbit                      | ✓ (Toggle                                                                                                                                                                                                                                                                                                                                                            | e I/F)                                                                                                                                                                                                                                                                                                                                                                            |

\* VccQ and Vcc may be distinct and unique voltages on Toggle I/F product. The device shall support one of the following VccQ/Vcc combinations,

Vcc = 3.3V, VccQ = 3.3V Vcc = 3.3V, VccQ = 1.8V

3.3V VccQ is not supported for the case where transfer rate is greater than 100MHz.

### ΚΙΟΧΙΑ

### 24nm Serial Interface NAND Package (2nd Generation)

| Туре                                 | WSON8                                                                                      |                                          |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------|--|--|--|

| Size<br>Vcc<br>Temp.<br>Pin<br>Pitch | 6 x 8mm<br>3.3V&1.8V<br>-40 to 85°C<br>8Pins<br>1.27mm                                     |                                          |  |  |  |

| Pin Assignment<br>(Top View)         | <ul> <li>○</li> <li>1) CS</li> <li>2) SO/IO1</li> <li>3) WP/IO2</li> <li>4) Vss</li> </ul> | Vcc 8<br>HOLD/IO3 7<br>SCK 6<br>SI/IO0 5 |  |  |  |

| Lineup                               | Serial Interface NAND                                                                      |                                          |  |  |  |

| 1Gbit                                | ✓                                                                                          |                                          |  |  |  |

| 2Gbit                                | $\checkmark$                                                                               |                                          |  |  |  |

| 4Gbit                                | $\checkmark$                                                                               |                                          |  |  |  |

| 8Gbit                                | $\checkmark$                                                                               |                                          |  |  |  |

KIOXIA

### **Our Mission**

# Uplifting the world with "memory"

By evolving "memory," we create uplifting experiences and change the world.

The name KIOXIA is a combination of the Japanese word *kioku* meaning "memory" and the Greek word *axia* meaning "value" – which forms the foundation of the company's vision.

Unleashing the potential of "memory" to create new value.

ΚΙΟΧΙΑ

## **Application Guide & Comments**

© 2021 KIOXIA Corporation. All Rights Reserved.

## **Reliability Guidance**

### **Overview**

This reliability guidance is intended to provide some guidance related to using NAND Flash memory. For detailed reliability data on each SLC NAND Flash memory product, please refer to the reliability note of the respective product.

Each NAND Flash memory cell has a floating gate which is isolated by the insulator, i.e. silicon dioxide. In the Write(Program) operation, the electrons are injected into the floating gate and the cell data is changed to '0'(zero). On the other hand, the electrons are ejected from the floating gate by the Erase operation and all of the cell data in this block is changed to '1'(one).

NAND Flash memory cells are gradually worn out and their reliability level is degraded by repeating the Write and Erase operations of '0' data in each block because electrons move in and out of the floating gate at each '0' data Write and Erase operation. The reliability of NAND Flash memory cells during the actual usage on system level depends on the usage and environmental conditions. KIOXIA adopts the checker pattern data, 0x55 & 0xAA for alternative Write/Erase cycles, for the reliability test.

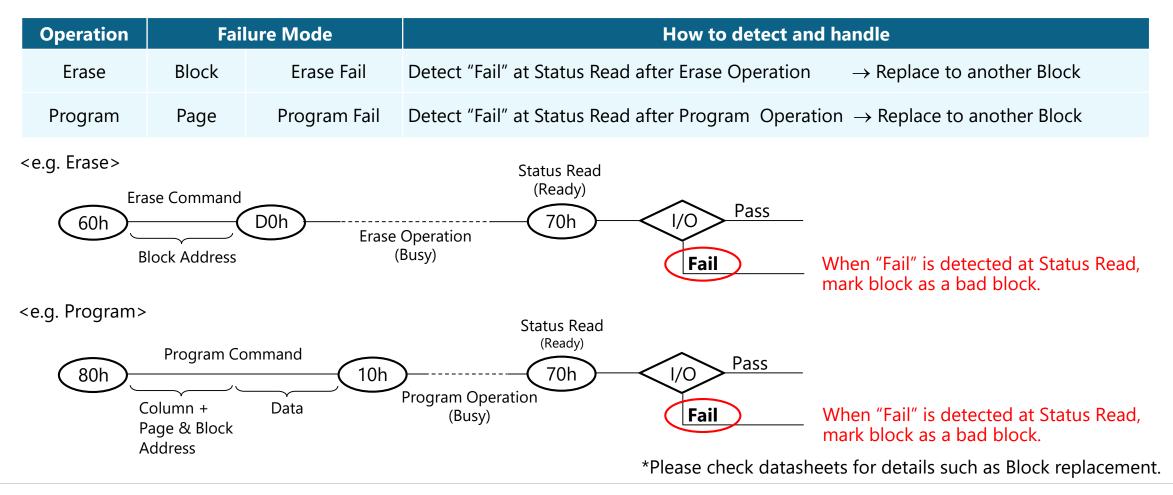

Generally, a block should be marked as bad when a program status failure or erase status failure is detected. Although random bit errors may occur during use, it does not necessarily mean that a block is bad.

NAND Flash memory management, including, but not limited to, Bad Block Management, ECC treatment and Wear Leveling, should be recognized and incorporated into system design. ECC treatment for read data is mandatory against random bit errors, and the host should monitor ECC status to take appropriate measures such as rewrite (Data Refresh) in consideration of Wear Leveling before an uncorrectable ECC error occurs. If such ECC treatment is not implemented, read failure due to random bit errors may occur even before program or erase status failure.

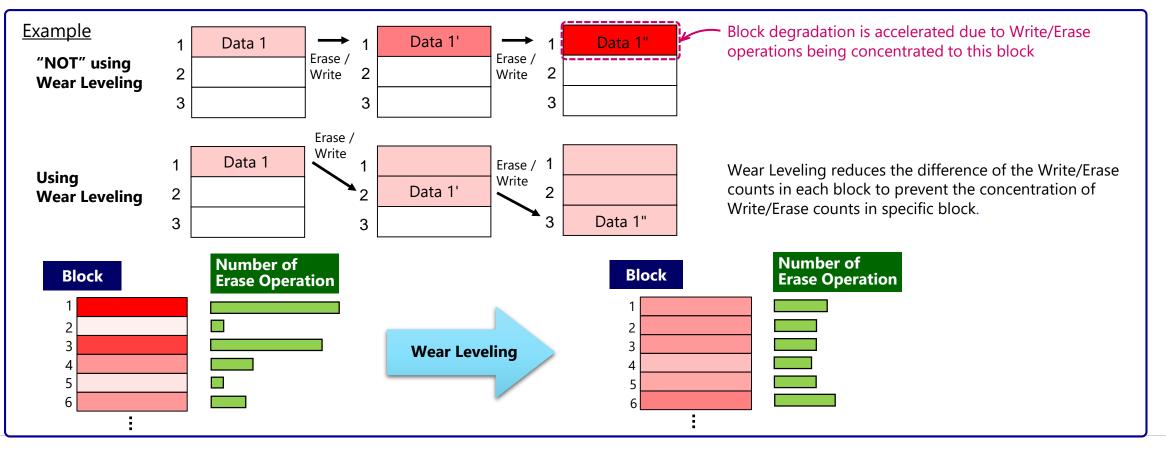

To realize a robust system design, it is generally necessary to prevent the concentration of Write/Erase cycles at specific blocks by adopting Wear Leveling, which manages to distribute Write/Erase cycles evenly among NAND Flash memory. It is also necessary to avoid dummy '0' data writes, e.g. '0' data padding, which accelerate block endurance degradation.

For details, please refer to the following pages which explain ideas to realize a robust system design based on NAND Flash memory reliability.

### Write/Erase Endurance

The cumulative bad block count will increase along with the number of Write/Erase cycles. Since <u>NAND Flash memory has a limitation regarding Write/Erase Endurance</u>, Write or Erase failure may occur in a cell, page, or block. These failures are detected by doing a status read after either an Auto Page Program or Auto Block Erase operation. To prevent a failure caused by the excessive number of Write/Erase cycles on a specific block, implementation of Wear Leveling by the host side is necessary to average the number of Write/Erase cycles to each block.

### **Data Retention**

The data in NAND Flash memory may change after a certain amount of storage time. This is due to charge loss or charge gain. After block erasure and reprogramming, the block may become usable again.

Data Retention time is generally influenced by the number of Write/Erase cycles and temperature.

To prevent read failure due to Data Retention, ECC treatment for read data is mandatory against random bit errors, and the host should monitor ECC status to take appropriate measures before an uncorrectable error occurs.

### **Read Disturb**

A Read operation may disturb the data in NAND Flash memory. The data may change due to charge gain. Usually, bit errors occur on other pages in the block, not the page being read. After a large number of read cycles (between block erases), a tiny charge may build up and can cause a cell to be soft programmed to another state. After block erasure and reprogramming, the block may become usable again. Read Disturb capability is generally influenced by the number of Write/Erase cycles. <u>A large number of read cycles (between block erases) requires careful attention.</u> To prevent read failure due to Read Disturb, ECC treatment for read data is mandatory against random bit errors, and the host should monitor ECC status to take appropriate measures before an uncorrectable error occurs.

\*For the detailed reliability data for each SLC NAND product, please refer to reliability note of respective product.

## SLC NAND Flash memory Management

NAND Flash memory realizes Gigabit class memory via advanced processing technology. When using the device, please understand that the reliability characteristics and NAND Flash memory management, including, but not limited to, Bad Block Management, ECC treatment and Wear Leveling, should be recognized and incorporated into the system design.

### **Bad Block Management**

There are two types of Bad Block.

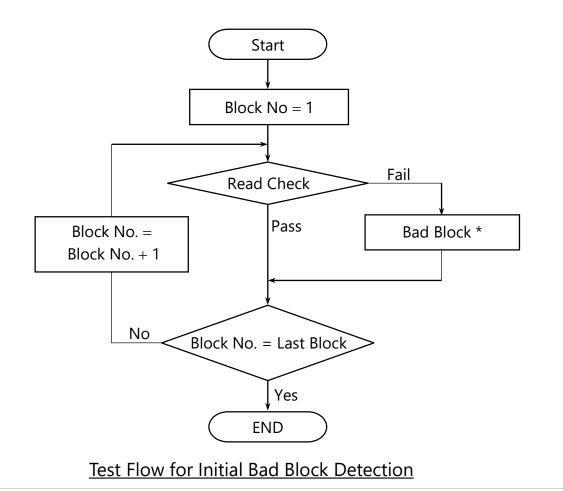

(a) Initial Bad Block

NAND Flash memory may contain unusable blocks at the time of brand-new state. These blocks are called Initial Bad Blocks. It is necessary to confirm if the product contains initial bad blocks at the point of first use, and DO NOT use those bad block.

< Example Test Flow for 24nm SLC NAND products >

Data in all pages are marked as '0' for the initial bad block. The user is able to detect the initial bad block with the Read Check operation to any column in a page for each block. If the data is 00h, this block should be marked as the bad block.

\* DO NOT execute the Erase operation to the detected bad blocks.

\* For Bad Block Test Flow of BENAND and Serial NAND devices during Read Check, regardless of the result of Status Read (ECC Pass or Fail), use the read data value to judge if it is a Bad Block.

#### (b) Acquired Bad Block

NAND Flash memory cells are gradually degraded by repeating the Write and Erase operations, and acquired bad blocks may occur during the Program or Erase operations. Acquired bad blocks are detected by doing a status read after either the Auto Page Program or Auto Block Erase operation. DO NOT use detected acquired bad blocks.

### KIOXIA

## **ECC (Error Correction Code)**

ECC treatment for read data is mandatory against random bit errors, and the host should monitor ECC status to take appropriate measures such as rewrite in consideration of Wear Leveling before an uncorrectable error occurs. **24nm 1Gbit/2Gbit/4Gbit/8Gb/16Gb SLC NAND requires 8bit/512Byte ECC** to be managed by the host controller. BENAND and Serial Interface NAND have an embedded hardware ECC engine. Using BENAND or Serial Interface NAND, it is possible for customers to use the latest 24nm SLC NAND flash memory technology even when their platform cannot support higher bit ECC.

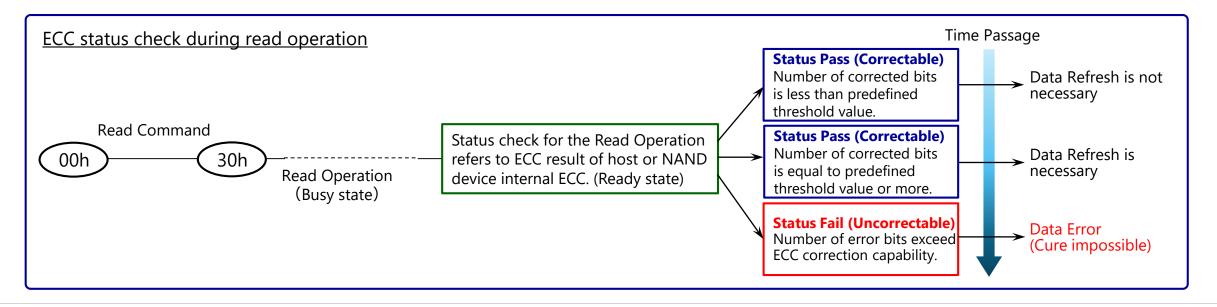

#### **Read status check during read operation**

In addition to after the Program and Erase operations, it is necessary to perform a status check during the Read operation. The status check for the Read operation is important to detect random bit errors due to data retention, read disturb, etc. and judge if the Data Refresh (Rewrite) operation is necessary.

#### ΚΙΟΧΙΑ

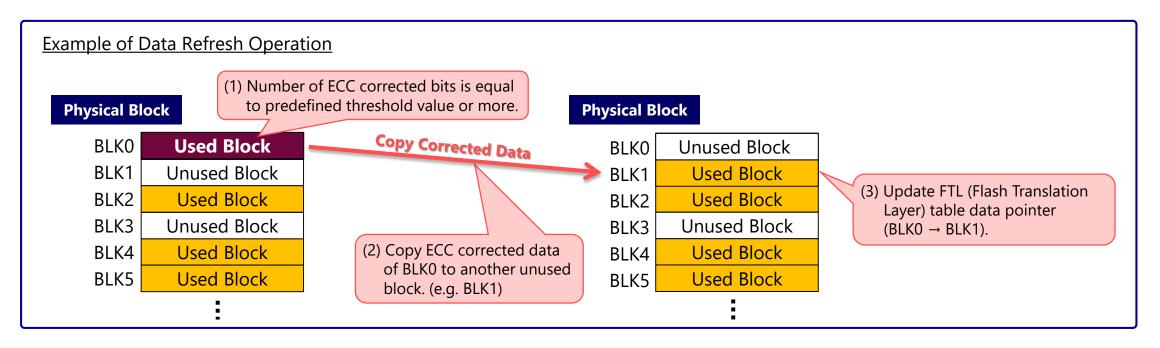

# **Data Refresh (Rewrite) Operation**

Data in NAND Flash memory may be changed due to Data Retention, Read Disturb, etc. Host should monitor ECC status to take appropriate measures such as Data Refresh by copying the corrected data to another unused block. The Data Refresh operation results in a higher reliability system against data error. Since Data Refresh conducts a Write/Erase operation, it is necessary to consider Wear Leveling.

Note : BENAND & Serial Interface NAND products have built in ECC functions and have command support for checking the internal ECC status.

- ✓ BENAND supports the Status Read (70h) and ECC Status Read (7Ah) commands.

- ✓ Serial NAND supports ECC Bit Flip Count Detection, ECC Bit Flip Count Report and ECC Maximum Bit Flip Count Report.

- For detail information, please refer to the respective product's datasheet.

#### ΚΙΟΧΙΑ

# **Averaging of Write/Erase Cycles Across Blocks (Wear Leveling)**

The number of Write/Erase operations in NAND Flash memory is limited. If Write/Erase operations are concentrated to specific blocks, it will accelerate the cell degradation at these blocks. Therefore, in usages with cycles of high amounts of Write/Erase operations, the measures should be implemented to ensure that Write/Erase operations are delivered evenly to each block among NAND Flash memory. In general, manage Write/Erase counts and then apply an averaging procedure such as Wear Leveling to prevent the concentration of Write/Erase operations to specific blocks. Wear Leveling should be managed at host side.

# Technical Considerations for SLC NAND Flash Memory Usage

# NAND Flash memory usage consideration 1

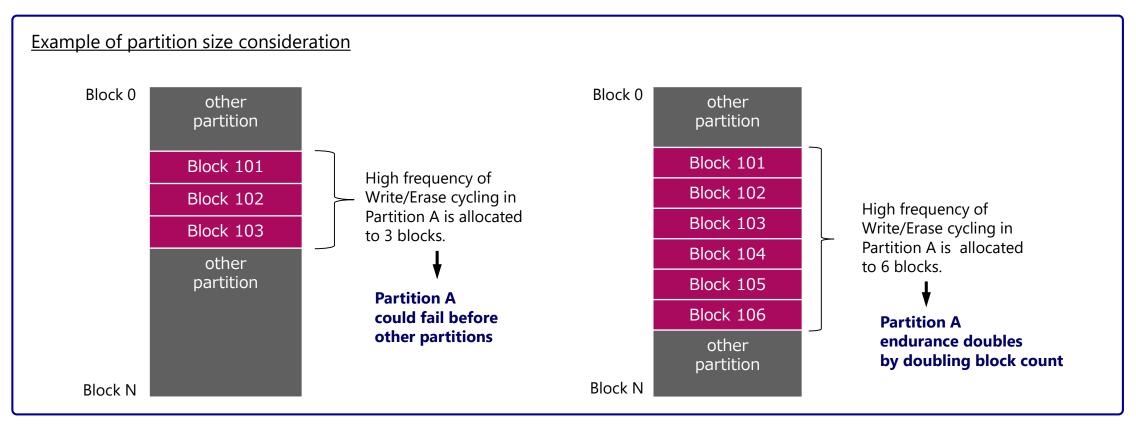

# Partition size considerations for high Write/Erase cycling partitions

An appropriate Wear Leveling algorithm should be used to avoid concentrated access to specific blocks. For partitions with high frequency Write/Erase cycling, it is necessary to allocate an adequate partition size with a sufficient number of blocks for Wear Leveling.

Insufficient partition size settings for high Write/Erase cycling partition can accelerate NAND cell degradation and cause such a partition to fail earlier than the other partitions.

With the same Wear Leveling, doubling the block count of a partition can double the Write/Erase endurance of the partition.

#### ΚΙΟΧΙΑ

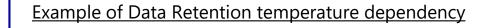

## **Temperature dependence of Data Retention**

The data in NAND Flash memory may change after a certain amount of storage time. The Data Retention time is influenced by Write/Erase cycles and temperature. At higher temperatures, the Data Retention capability of NAND Flash memory degrades.

For specific Write/Erase cycles = N cycles and different temperatures, Data Retention time varies as X > Y > Z years.

- \* If the operating environment includes higher temperatures, the effect of higher temperatures on data retention of NAND Flash memory should be recognized and appropriate design measures, such as data refresh, should be implemented to meet the target system reliability and improve overall reliability.

- \* If necessary, please request the Data Retention graph for higher temperatures to KIOXIA.

#### KIOXIA

#### SUBJECT TO CHANGE WITHOUT NOTICE <For Recipient Eyes Only>

M2PLZ00-1026 January, 2021

**Confidential**

## NAND Flash memory cell data consideration for NAND cell reliability

A NAND Flash memory cell has a value of '1' when erased and a value of '0' when programmed.

In general, programming a '0' bit to a NAND cell causes greater stress to the NAND cell than programming a '1' bit.

When programming a '0' bit, the electrons are injected into the floating gate and the cell data is changed to '0'(zero).

On the other hand, if in an Erase operation the electrons are ejected from the floating gate, then all of the cell data in this block will be '1'(one). Therefore it is necessary to avoid dummy '0' data write, e.g. '0' data padding.

If there is a high percentage of fixed '0' bits in the data pattern along with continuous Write and Erase cycling, it can lead to faster block endurance degradation.

| <u>Example: NA</u> | Example: NAND cell array with '0' data padding          1       : "1" data cell       0       : "0" data cell |   |   |   |   |   |               |             |                               |           |              |             |                                                     |              |       |             |    |   |   |   |     |   |   |   |   |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---------------|-------------|-------------------------------|-----------|--------------|-------------|-----------------------------------------------------|--------------|-------|-------------|----|---|---|---|-----|---|---|---|---|--|--|--|

|                    | 0                                                                                                             | 1 | 0 | 0 | 1 | 0 | 0             | 0           | 0                             | 0         | 0            | 0           | 0                                                   | 1            | (     | 0           | 0  | 1 | 1 | 1 | 1   | 1 | 1 | 1 | 1 |  |  |  |

|                    | 0                                                                                                             | 1 | 0 | 1 | 1 | 0 | 0             | 0           | 0                             | 0         | 0            | 0           | 0                                                   | 1            | (     | 0           | 1  | 1 | 1 | 1 | 1   | 1 | 1 | 1 | 1 |  |  |  |

|                    | 1                                                                                                             | 0 | 1 | 0 | 0 | 0 | 0             | 0           | 0                             | 0         | 0            | 0           | 1                                                   | C            | )     | 1           | 0  | 0 | 1 | 1 | 1   | 1 | 1 | 1 | 1 |  |  |  |

|                    | 1                                                                                                             | 1 | 0 | 0 | 1 | 0 | 0             | 0           | 0                             | 0         | 0            | 0           | 1                                                   | 1            | (     | 0           | 0  | 1 | 1 | 1 | 1   | 1 | 1 | 1 | 1 |  |  |  |

|                    | 0                                                                                                             | 0 | 1 | 1 | 0 | 0 | 0             | 0           | 0                             | 0         | 0            | 0           | 0                                                   | 0            |       | 1           | 1  | 0 | 1 | 1 | 1   | 1 | 1 | 1 | 1 |  |  |  |

|                    | 1                                                                                                             | 0 | 1 | 0 | 1 | 0 | 0 0 0 0 0 0 0 |             |                               |           |              | 0           | 1     0     1     0       0     1     0     1     0 |              |       | 1 1 1 1 1 1 |    |   | 1 | 1 | 1 1 |   |   |   |   |  |  |  |

|                    | 0                                                                                                             | 1 | 0 | 1 | 0 | 0 | 0             | 0 0 0 0 0 0 |                               |           |              | 0           |                                                     |              |       | 1           | 0  | 1 | 1 | 1 | 1   | 1 | 1 | 1 |   |  |  |  |

|                    | 1                                                                                                             | 0 | 1 | 0 | 1 | 0 | 0             | 0           | 0                             | 0         | 0            | 0 0         |                                                     |              |       | 1           | 0  | 1 | 1 | 1 | 1   | 1 | 1 | 1 | 1 |  |  |  |

|                    |                                                                                                               |   |   |   |   |   |               |             |                               |           |              |             |                                                     |              |       |             |    |   |   |   |     |   |   |   |   |  |  |  |

|                    | User data area Remaining area                                                                                 |   |   |   |   |   |               |             | User data area Remaining area |           |              |             |                                                     |              |       |             |    |   |   |   |     |   |   |   |   |  |  |  |

|                    | (a) Accelerate block endurance degradation by fixed dummy "0" data write                                      |   |   |   |   |   |               |             | (b                            | )"1<br>(R | " da<br>lecc | ata f<br>mm | for R<br>nend                                       | Rema<br>led) | ainin | g ar        | ea |   |   |   |     |   |   |   |   |  |  |  |

# NAND Flash memory usage consideration 4

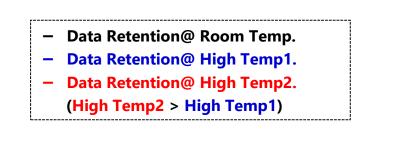

## Shadowing technique to improve performance and reduce Read Disturb stress

When the frequency of read cycles (between block erases) is estimated to be high, apply procedures such as block erasure and reprogramming (refer to Data Refresh (Rewrite) Operation) or data copy into RAM (e.g. DRAM, SRAM) to prevent the concentration of Read access to NAND Flash memory.

Shadowing is the process in which data stored in NAND Flash memory (e.g. program / image code such as frequently accessed read data) is copied to RAM during system initialization. Once the data is copied, the data is read out from the RAM to prevent the concentration of Read access to NAND Flash memory.

Expected Benefits of Shadowing

- Since Read access speed from RAM is generally faster than that of NAND Flash memory, it can be expected to improve system performance.

- By copying the data to RAM during system initialization and reading the data from RAM during system operation, it is possible to reduce the Read access to NAND Flash memory. As a result, improvement of reliability against data errors such as Read Disturb can be expected.

# **RESTRICTIONS ON PRODUCT USE**

KIOXIA Corporation and its subsidiaries and affiliates are collectively referred to as "KIOXIA".

Hardware, software and systems described in this document are collectively referred to as "Product".

- KIOXIA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from KIOXIA. Even with KIOXIA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though KIOXIA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant KIOXIA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "Reliability Information" in KIOXIA Corporation's website and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. KIOXIA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, and devices related to power plant. IF YOU USE PRODUCT FOR UNINTENDED USE, KIOXIA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your KIOXIA sales representative or contact us via our website.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by KIOXIA for any infringement of patents or any other intellectual

property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel

or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, KIOXIA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your KIOXIA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all

applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. KIOXIA ASSUMES NO LIABILITY FOR

DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

#### KIOXIA

M2PLZ00-1026 January, 2021 **Confidential**

# KIOXIA

# **UFS & e-MMC Roadmap**

Aug. 2021

Memory Application Engineering Dept. 1 Memory Division KIOXIA Corporation

© 2021 KIOXIA Corporation. All Rights Reserved.

M1PCZ00-283 June., 2021

# **UFS & e-MMC Overview**

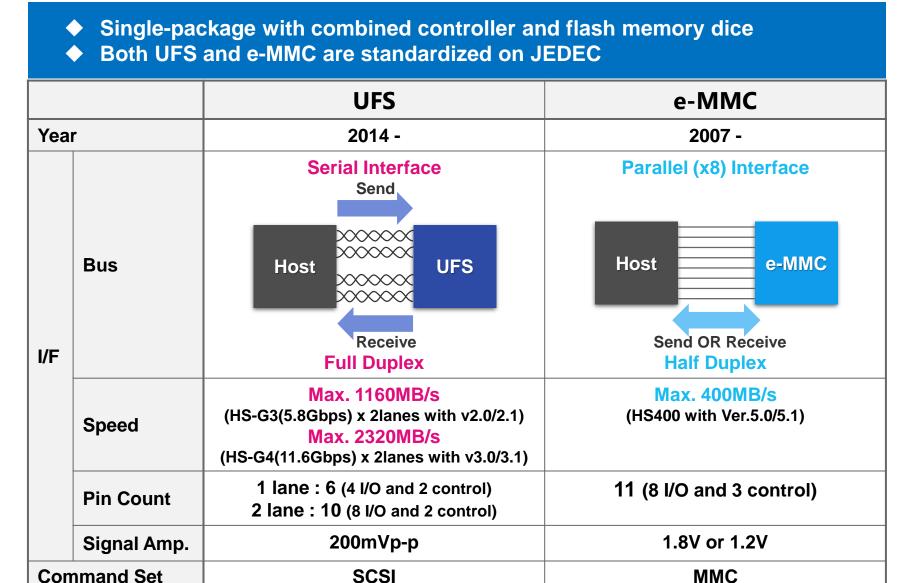

# **UFS & e-MMC Introduction**

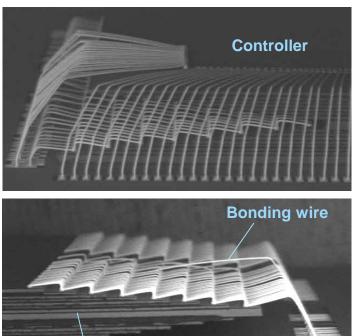

e.g. 153ball BGA, 11.5x13mm, 0.5mm ball pitch

NAND (16 dice stacked)

SUBJECT TO CHANGE WITHOUT NOTICE For Recipient Eyes Only

**KIOXIA** Confidential

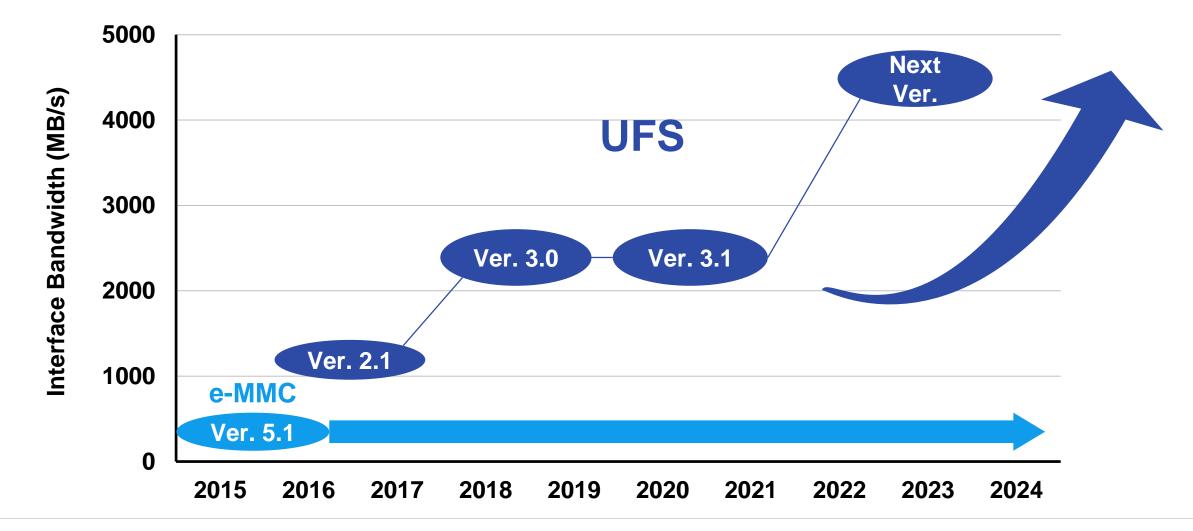

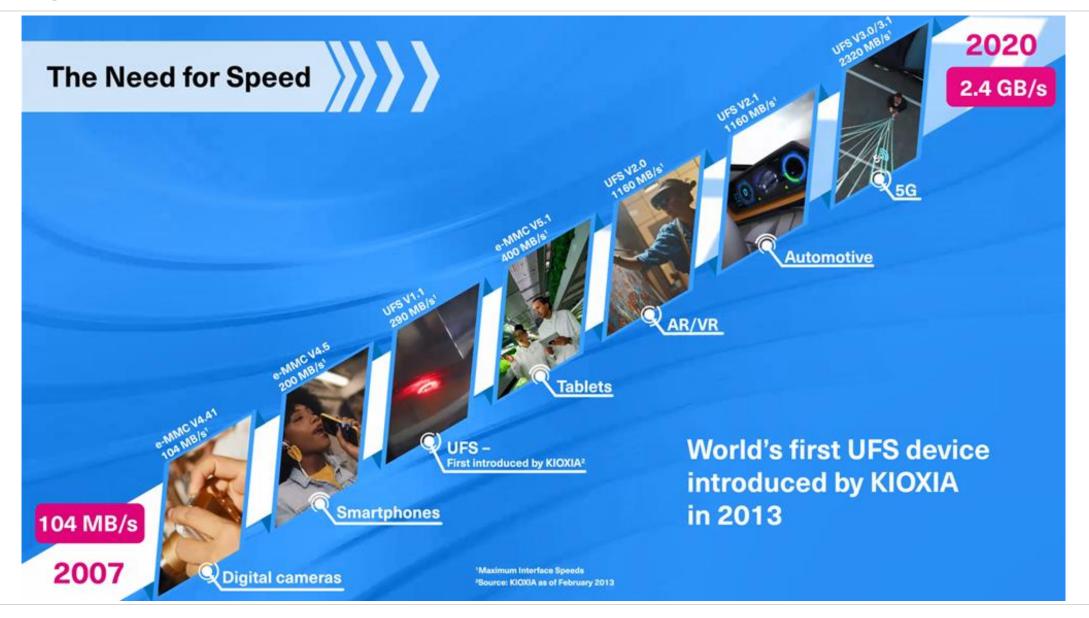

# **UFS & e-MMC Interface Bandwidth**

# UFS has a great scalability

ΚΙΟΧΙΑ

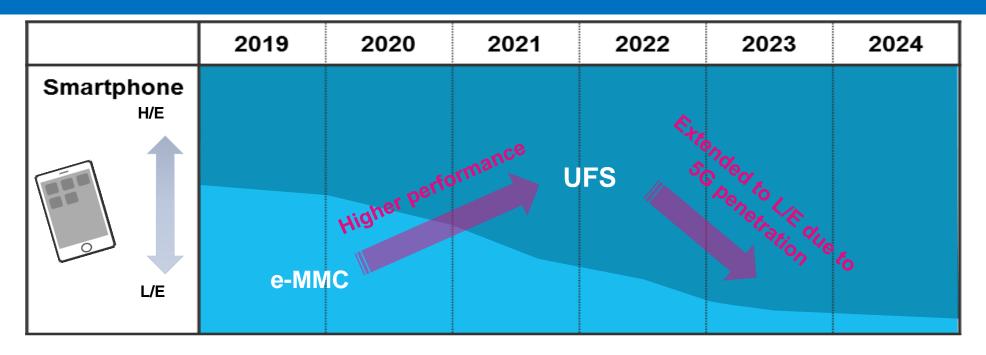

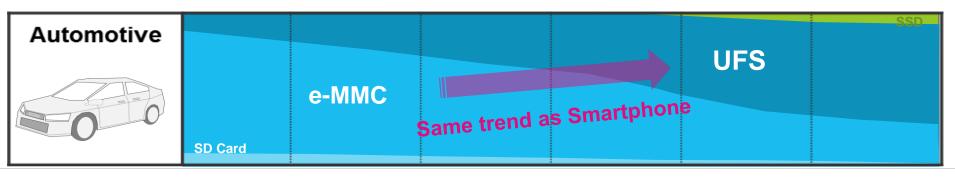

# UFS interface is widely spreading over smartphone and automotive applications

ΚΙΟΧΙΑ

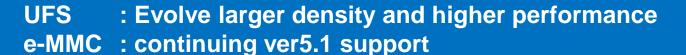

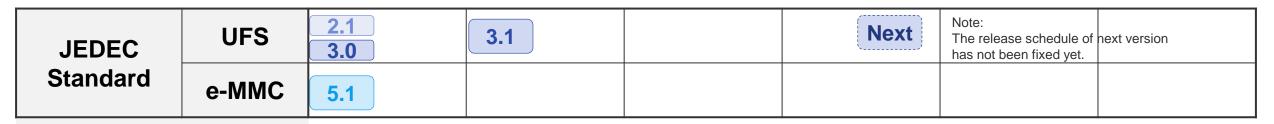

# **UFS & e-MMC Technology Roadmap**

M1PCZ00-283 June., 2021

| -    |      |      |      |      |      |

|------|------|------|------|------|------|

| 0040 | 0000 | 0004 | 0000 | 0000 | 0004 |

| 2019 | 2020 | 2021 | 2022 | 2023 | 2024 |

|      |      |      |      |      |      |

Note: 4GB e-MMC is compliant with JEDEC Ver.5.0.

This roadmap does not specify EOL of each generation. EOL should be discussed and decided in good faith between the customer and KIOXIA

# **Managed FLASH evolution**

ΚΙΟΧΙΑ

SUBJECT TO CHANGE WITHOUT NOTICE For Recipient Eyes Only

**KIOXIA** Confidential

M1PCZ00-283

# UFS Lineup \* Please contact your local sales to make sure of the availability of UFS2.1/3.0 products

| Grade                               | UFS Ver. | Generation  | Density                                      | Part Number                             | qTotalRawDevice<br>Capacity | Boot LU<br>(Max.)                                       | RPMB LU           | PKG (mm)     |  |

|-------------------------------------|----------|-------------|----------------------------------------------|-----------------------------------------|-----------------------------|---------------------------------------------------------|-------------------|--------------|--|

|                                     |          |             | 32GB THGAF8G8T23BAIL 32,015,122,432 Byte 64M |                                         |                             |                                                         |                   | 11.5x13x0.8  |  |

|                                     | 0.4*     |             | 64GB                                         | THGAF8G9T43BAIR                         | 64,005,079,040 Byte         |                                                         | ] [               |              |  |

|                                     | 2.1*     | Gen6 -      | 128GB                                        | THGAF8T0T43BAIR                         | 127,984,992,256 Byte        | 128MB                                                   |                   | 11.5x13x1.0  |  |