# 3.5V to 36V, 3A, Synchronous Step-Down Regulator

#### **1 FEATURES**

- Automotive AEC-Q100 Grade 1 Compliance

- Wide V<sub>IN</sub> Range: 3.5V to 36V

- Wide V<sub>OUT</sub> Range: 1V to V<sub>IN</sub>

- Integrated both High-Side and Low-Side Power MOSFETs with up to 3A Output Capability

- Frequency Options: 400kHz, 1MHz, 2.1MHz

- PLL Synchronization to External Clock

- High Efficiency Low Load DCM and PFM Operation

- Near 100% Duty Cycle Operation for Low Drop Out Operation

- Forced PWM Option

- Accurate Peak and Valley Clamp and Protection

- Internal Compensation

- Spread Spectrum Option for Low EMI Applications

- Accurate VIN UVLO Protection

- Over-Temperature Shutdown and Recovery

- Operating Junction Temperature -40°C to 150 °C

- Output Short-Circuit Protection with Hiccup Mode

- Thermally Enhanced SOIC-EP8 Package (4.9mm X 3.9mm)

#### 2 APPLICATIONS

- Automotive Power Supplies

- Industrial Power Supplies

- Battery Powered Systems

#### 3 DESCRIPTION

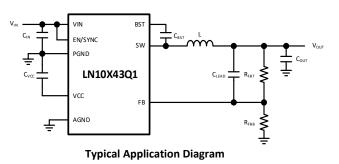

The LN10X43Q1 is a high efficiency, compact, synchronous step-down DC-DC converter employing a constant frequency, peak current mode control architecture with internal compensation. It operates from an input voltage from 3.5V to 36V, provides an adjustable output voltage from 1V to  $V_{IN}$ . LN10X43Q1 can deliver up to 3.0A. The nominal switching frequency is fixed on 400kHz, 1MHz or 2.1MHz, or can be synchronized to an external clock. Automatic frequency foldback at light load can improve efficiency.

Additional features such as FPWM option, precision enable, and internal soft start provide both flexible and easy to use solutions for a wide range of applications. Protection features include input undervoltage lockout, thermal shutdown, cycle-by-cycle current limit, and short-circuit protection.

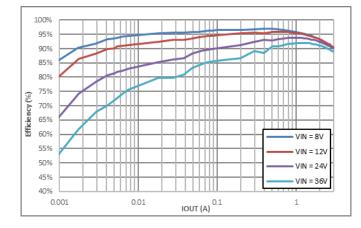

LN10043Q1, Vout=5V, Efficiency Curve

# **Table of Contents**

| 1 | F    | EATURES                                | 1    |

|---|------|----------------------------------------|------|

| 2 | A    | PPLICATIONS                            | 1    |

| 3 | D    | ESCRIPTION                             | 1    |

| 4 | R    | EVISION HISTORY                        | 3    |

| 5 | С    | RDER INFORMATION                       | 4    |

| 6 | Р    | IN CONFIGURATION                       | 5    |

|   | 6.1  | Pin Configuration                      | 5    |

|   | 6.2  | Pin Functions                          | 5    |

| 7 | S    | PECIFICATIONS                          | 6    |

|   | 7.1  | Absolute Maximum Ratings               | 6    |

|   | 7.2  | ESD Ratings                            | 6    |

|   | 7.3  | Recommented Operating Condition        | 6    |

|   | 7.4  | Package Thermal Parameters             | 7    |

|   | 7.5  | Electrical Characteristics             | 8    |

|   | 7.6  | Typical Characteristics                | . 11 |

| 8 | F    | UNCTIONAL DESCRIPTION                  | . 16 |

|   | 8.1  | Overview                               | . 16 |

|   | 8.2  | Funtional Diagram                      | . 17 |

|   | 8.3  | Application Diagram with Full Features | . 17 |

|   | 8.4  | Funtional Description                  | . 18 |

| 9 | A    | PPLICATION INFORMATON                  | . 21 |

|   | 9.1  | Typical Applications                   | . 21 |

| 1 | 0 L  | AYOUT                                  |      |

|   | 10.1 | Layout Guidelines                      | . 22 |

| 1 | 1 P  | ACKAGE INFORMATION                     | . 24 |

|   | 11.1 | Package Outline                        | . 24 |

|   | 11.2 | Pootprint Example                      | . 25 |

|   |      | RTANT NOTICE AND DISCLAIMERS           |      |

| E | NVIR | ONMENTAL DECLARATION                   | . 26 |

## **4 REVISION HISTORY**

| Version | Change Description                                                                                                                                                                                                                   | Date       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.0     | Initial Version                                                                                                                                                                                                                      | 2021/10/28 |

| 1.1     | Update Part Number throughout the document ·····P4<br>Tighten the min, max and typical limits of electrical parameters·····P8<br>Add switching waveform in SPREAD SPECTRUM MODULATION·····P13<br>Update package information ·····P24 | 2022/4/24  |

LEN LEN Technology LTD.

# 5 ORDER INFORMATION

| Part Number   | Frequency | Light Load<br>Mode | Spread<br>Spectrum | IC<br>Package | MSL-<br>Peak-<br>Temp <sup>(1)</sup> | Material | Package        | Package<br>Qty | Top<br>Marking <sup>(2)</sup> |

|---------------|-----------|--------------------|--------------------|---------------|--------------------------------------|----------|----------------|----------------|-------------------------------|

| LN10043Q1-EFR | 400kHz    | PFM                | No                 | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | LN10043Q1                     |

| LN10143Q1-EFR | 400kHz    | FPWM               | No                 | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | LN10143Q1                     |

| LN10243Q1-EFR | 1MHz      | PFM                | No                 | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | LN10243Q1                     |

| LN10343Q1-EFR | 1MHz      | FPWM               | No                 | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | LN10343Q1                     |

| LN10443Q1-EFR | 2.1MHz    | PFM                | No                 | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | LN10443Q1                     |

| LN10543Q1-EFR | 2.1MHz    | FPWM               | No                 | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | LN10543Q1                     |

| LN10043Q1SEFR | 400kHz    | PFM                | Yes                | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | 10043QS                       |

| LN10143Q1SEFR | 400kHz    | FPWM               | Yes                | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | 10143QS                       |

| LN10243Q1SEFR | 1MHz      | PFM                | Yes                | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | 10243QS                       |

| LN10343Q1SEFR | 1MHz      | FPWM               | Yes                | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | 10343QS                       |

| LN10443Q1SEFR | 2.1MHz    | PFM                | Yes                | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | 10443QS                       |

| LN10543Q1SEFR | 2.1MHz    | FPWM               | Yes                | SOIC-<br>EP8  | Level-3-<br>260C                     | RoHS     | Tape &<br>Reel | 3000           | 10543QS                       |

(1) MSL (Moisture Sensitivity Level) is based on JEDEC industrial classification and the tabled temperature is the maximum solder temperature;

(2) There may be additional marking relates to the lot number or date code on the device.

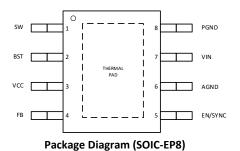

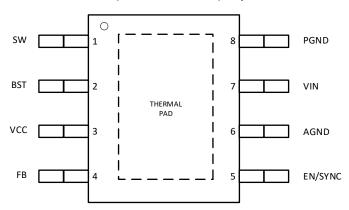

## 6 **PIN CONFIGURATION**

# 6.1 Pin Configuration

SOIC-EP8 (4.9mm X 3.9mm) Top View

# 6.2 Pin Functions

| Name                | PIN<br>Number                                                                                                              | Туре   | Description                                                                                                                                                                                                                                                               |

|---------------------|----------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW                  | 1                                                                                                                          | Power  | Switch node connection from the internal power MOSFETs to the external inductor.                                                                                                                                                                                          |

| BST                 | Bootstrapped supply to the high side gate driver. Connect a $0.1$ - $0.47\mu F$ ceramic capacitor between BST and SW pins. |        |                                                                                                                                                                                                                                                                           |

| V() 3 Power - · · · |                                                                                                                            |        | Voltage source that powers the gate drivers of the internal power MOSFETs and control circuits. Must be decoupled to PGND with a $1 - 4.7\mu$ F ceramic capacitor.                                                                                                        |

| FB                  | 4                                                                                                                          | Signal | Output voltage feedback input. Use an external divider to set the desired output voltage.                                                                                                                                                                                 |

| EN/SYNC             | 5                                                                                                                          | Signal | Enable pin for V <sub>CC</sub> LDOs, regulator output, and input voltage for V <sub>IN</sub> UVLO. Connect to V <sub>IN</sub> directly, to V <sub>IN</sub> through a divider, or to an external voltage source. This pin is also used for external clock synchronization. |

| AGND                | 6                                                                                                                          | Ground | Analog ground.                                                                                                                                                                                                                                                            |

| VIN                 | 7                                                                                                                          | Power  | Power supply input pin to high side power MOSFET and $V_{\text{IN}}$ LDO regulator. Decouple this pin to PGND with ceramic capacitors.                                                                                                                                    |

| PGND                | 8                                                                                                                          | Ground | Power ground. Connect the pins to ground plane.                                                                                                                                                                                                                           |

| THERMAL<br>PAD      | -                                                                                                                          | -      | Thermal dissipation pad. Solder to ground plane.                                                                                                                                                                                                                          |

# **7** SPECIFICATIONS

## 7.1 Absolute Maximum Ratings

| Parameters <sup>(1)</sup>             | Min  | Max                   | Unit |

|---------------------------------------|------|-----------------------|------|

| VIN to PGND                           | -0.3 | 42                    |      |

| EN/SYNC to PGND                       | -0.3 | V <sub>IN</sub> + 0.3 |      |

| FB to AGND                            | -0.3 | 5.5                   | , v  |

| SW to PGND                            | -1.0 | V <sub>IN</sub> + 0.3 | V    |

| SW to PGND (Less than 10ns overshoot) | -3.5 | 42                    |      |

| BST to SW                             | -0.3 | 5.5                   |      |

| Operating Ambient Temperature         | -40  | 125                   |      |

| Junction Temperature                  | -40  | 150                   | °C   |

| Storage Temperature                   | -55  | 150                   |      |

(1) Exceeding these absolute-maximum-ratings may damage the device.

# 7.2 ESD Ratings

| Parameters              | Min | Max   | Unit |

|-------------------------|-----|-------|------|

| HBM Human Body Model    |     | ±3000 | N/   |

| CDM Charge Device Model |     | ±750  | v    |

# 7.3 Recommented Operating Condition

| Parameters           | Min  | Max             | Unit |

|----------------------|------|-----------------|------|

| VIN                  | 3.5  | 36              |      |

| EN/SYNC              | -0.3 | V <sub>IN</sub> | V    |

| FB                   | -0.3 | 1.1             |      |

| VOUT                 | 1    | V <sub>IN</sub> |      |

| IOUT                 | 0    | 3               | А    |

| Junction Temperature | -40  | 150             | °C   |

# 7.4 Package Thermal Parameters

|                  | Parameter <sup>(1)</sup>                   | SOIC-EP8 | Units |

|------------------|--------------------------------------------|----------|-------|

| R <sub>θJA</sub> | Junction-to-Ambient Thermal Resistance     | 39       | °C/W  |

| Ψ,π              | Junction-to-Top Characterization Parameter | 3        | °C/W  |

(1) Measurements are based on standard 2s2p PCB defined in JESD 51-7 2s2p, under no wind , 2W loss, and 25 °C ambient temperature.

LEN LEN Technology LTD.

# 7.5 Electrical Characteristics

Unless otherwise stated, the minimum and maximum limits apply over the recommended operating junction temperature range of -40°C to 150°C. Typical values are measured at 25°C and represent the most likely norm. The default conditions apply:  $V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $F_S = 400$ kHz.

| SYMBOL                             | PARAMETER                                      | CONDITION                                                                             | MIN   | ТҮР  | MAX   | UNIT |

|------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------|-------|------|-------|------|

| SUPPLY VC                          | DLTAGE, VOUT (VIN PINS)                        |                                                                                       |       |      |       |      |

| V <sub>IN</sub>                    | Operating Input Voltage<br>Range               |                                                                                       | 3.5   |      | 36    | v    |

| I <sub>Q-PFM-NOSW</sub>            | Operating Quiescent Current<br>(Non-Switching) | V <sub>FB</sub> =1.2V, T <sub>A</sub> =25°C                                           |       | 62   |       | μA   |

| I <sub>Q-FPWM</sub> <sup>(1)</sup> | During Regulation In FPWM                      | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 5V, I <sub>OUT</sub> = 0A<br>For LN10143Q1  |       | 4.38 |       | mA   |

| I <sub>SHDN</sub>                  | Shutdown Quiescent Current                     | V <sub>IN</sub> = 12V, V <sub>EN</sub> = 0V                                           |       | 0.5  | 4.05  | μΑ   |

| FB PIN                             |                                                |                                                                                       |       |      |       |      |

|                                    |                                                | Full V <sub>IN</sub> Range, Full Load Range,<br>@25°C                                 | 0.992 | 1.0  | 1.008 | V    |

| V <sub>FB-CCM</sub>                | Regulated Feedback Voltage in CCM Mode         | Full V <sub>IN</sub> Range, Full Load Range,<br>Full Operational Temperature<br>Range | 0.98  | 1.0  | 1.02  | V    |

| I <sub>Q-FB</sub>                  | Feedback Input Leakage<br>Current              | V <sub>FB</sub> = 1.0 V                                                               |       | 0    | 100   | nA   |

| POWER M                            | OSFETS <sup>(2)</sup>                          |                                                                                       |       |      |       |      |

| R <sub>DSON-HS</sub>               | High Side MOSFET ON<br>Resistance              | $I_{OUT} = 1A, V_{BST}-V_{SW} = 5V$                                                   |       | 148  | 260   | mΩ   |

| R <sub>DSON-LS</sub>               | Low Side MOSFET ON<br>Resistance               | I <sub>OUT</sub> = 1A, V <sub>CC</sub> = 5V                                           |       | 85   | 150   | mΩ   |

| PWM                                |                                                |                                                                                       |       |      |       |      |

| T <sub>ON-MIN</sub> <sup>(1)</sup> | Minimum ON Time                                |                                                                                       |       | 103  |       | ns   |

| OSCILLATO                          | DR                                             |                                                                                       |       |      |       |      |

| F <sub>S-400kHz</sub>              | For LN10043Q1& LN10143Q1                       |                                                                                       | 320   | 400  | 460   | kHz  |

| F <sub>S-1000kHz</sub>             | For LN10243Q1& LN10343Q1                       |                                                                                       | 800   | 1000 | 1150  | kHz  |

| F <sub>S-2100kHz</sub>             | For LN10443Q1& LN10543Q1                       |                                                                                       | 1700  | 2100 | 2450  | kHz  |

#### **Electrical Characteristics (Continued)**

Unless otherwise stated, the minimum and maximum limits apply over the recommended operating junction temperature range of -40°C to 150°C. Typical values are measured at 25°C and represent the most likely norm. The default conditions apply:  $V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $F_S = 400$ kHz.

| SYNCHRON                              | IZATION (EN/SYNC PIN)                         |                         |      |      |      |     |

|---------------------------------------|-----------------------------------------------|-------------------------|------|------|------|-----|

| F <sub>SYNC</sub> <sup>(3)</sup>      | SYNC Frequency Range                          |                         | 0.2  |      | 2.1  | MHz |

| V <sub>SYNC-HIGH</sub> <sup>(4)</sup> | SYNC High-Level Voltage                       |                         | 2.5  |      |      | V   |

| V <sub>SYNC-LOW</sub>                 | SYNC Low-Level Voltage                        |                         |      |      | 0.4  | V   |

| SPREAD SP                             | ECTRUM MODULATION <sup>(5)</sup>              |                         |      |      | ·    |     |

| %ΔFs                                  | Spread Spectrum Modulation<br>Frequency Range |                         |      | -20  |      | %   |

| F <sub>SSM</sub>                      | Spread Spectrum Modulation<br>Frequency       |                         |      | 13   |      | kHz |

|                                       | UVLO (EN PIN)                                 |                         |      |      | ·    |     |

| EN <sub>VOUT-ON</sub>                 | V <sub>IN</sub> UVLO Rising Threshold         | V <sub>EN</sub> Rising  | 1.70 | 1.88 | 2.05 | V   |

| EN <sub>VOUT-HYS</sub>                | V <sub>IN</sub> UVLO Hysteresis               | V <sub>EN</sub> Falling |      | 350  |      | mV  |

| I <sub>Q-EN</sub>                     | EN Pin Current                                | V <sub>EN</sub> = 3.3V  |      | 0    | 100  | nA  |

|                                       | /CC LDOS (VCC PIN)                            |                         |      |      | ·    |     |

| V <sub>CC-TARGET</sub>                | V <sub>cc</sub> Regulation Target             |                         |      | 4.75 |      | V   |

| BOOTSTRA                              | P (BST PIN) <sup>(1)</sup>                    |                         |      |      |      |     |

| t <sub>refresh-per</sub>              | Auto-Refresh Period                           |                         |      | 29   |      | μs  |

| t <sub>REFRESH-PUL</sub>              | Auto-Refresh Pulse Width                      |                         |      | 200  |      | ns  |

#### **Electrical Characteristics (Continued)**

Unless otherwise stated, the minimum and maximum limits apply over the recommended operating junction temperature range of -40°C to 150°C. Typical values are measured at 25°C and represent the most likely norm. The default conditions apply:  $V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $F_S = 400$ kHz.

| OVER CURRENT                      | PROTECTION <sup>(6)</sup>                          |                       |     |      |     |    |

|-----------------------------------|----------------------------------------------------|-----------------------|-----|------|-----|----|

| ILIM-PEAK-PFM                     | Peak Current Limit<br>Threshold in PFM             | V <sub>IN</sub> = 12V | 3.9 | 4.7  | 5.5 | А  |

| ILIM-PEAK-FPWM                    | Peak Current Limit<br>Threshold in FPWM            | V <sub>IN</sub> = 12V | 3.9 | 4.7  | 5.5 | А  |

| ILIM-Valley-PFM                   | Valley Current Limit<br>Threshold in PFM           | V <sub>IN</sub> = 12V | 2.9 | 3.2  | 3.5 | А  |

| ILIM-Valley-FPWM                  | Valley Current Limit<br>Threshold in FPWM          | V <sub>IN</sub> = 12V | 2.9 | 3.2  | 3.5 | А  |

| I <sub>NLIM-Valley-FPWM</sub> (1) | Negative Valley Current<br>Limit Threshold in FPWM | V <sub>IN</sub> = 12V |     | -1.5 |     | А  |

| THERMAL SHUT                      | DOWN <sup>(1)</sup>                                |                       |     |      |     |    |

| ОТ                                | Thermal Shutdown<br>Threshold                      |                       |     | 170  |     | °C |

| OT <sub>HYS</sub>                 | Thermal Shutdown<br>Recovery Hysteresis            |                       |     | -10  |     | °C |

| INTERNAL SOFT                     | START <sup>(7)</sup>                               |                       |     |      |     |    |

| t <sub>ss-int</sub>               | Soft-Start Time                                    |                       |     | 6    |     | ms |

(1) Guaranteed by design.

(2) Measured at pins.

(3) Tested with a 0V to +5Vpp, 50% duty cycle square wave.

(4) The average voltage on EN/SYNC pin must exceed EN<sub>VOUT-ON</sub>.

(5) This function is available on LN10X43Q1S only.

(6) This current limit was tested as the internal comparator trigger point, the current limits measured in a close loop application may be different.

(7) Measured from  $EN_{VOUT-ON}$  to internal soft start completed.

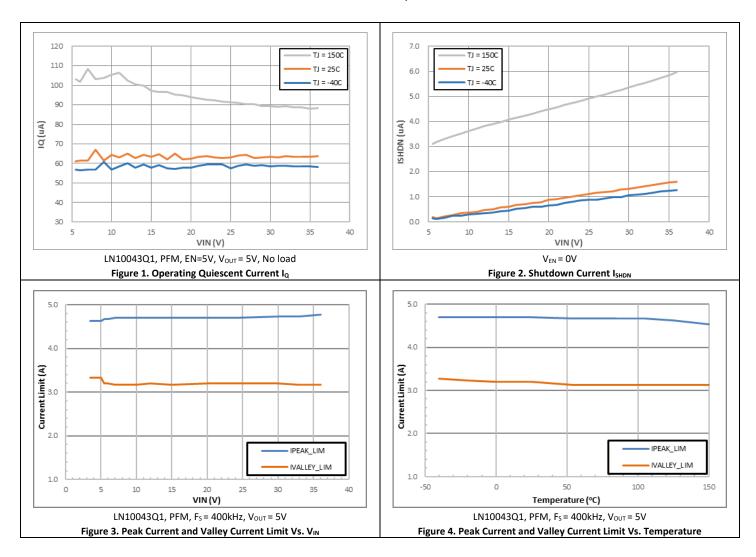

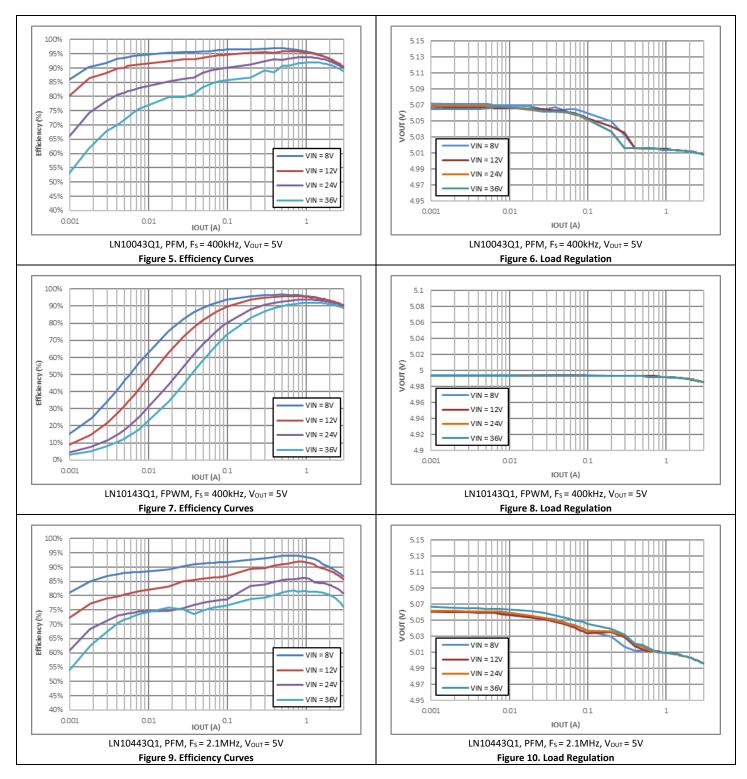

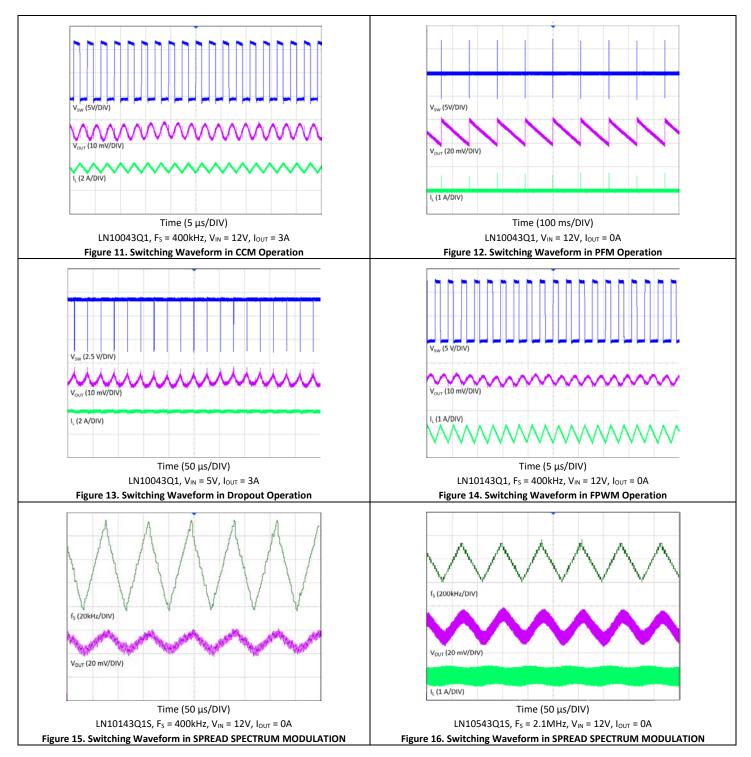

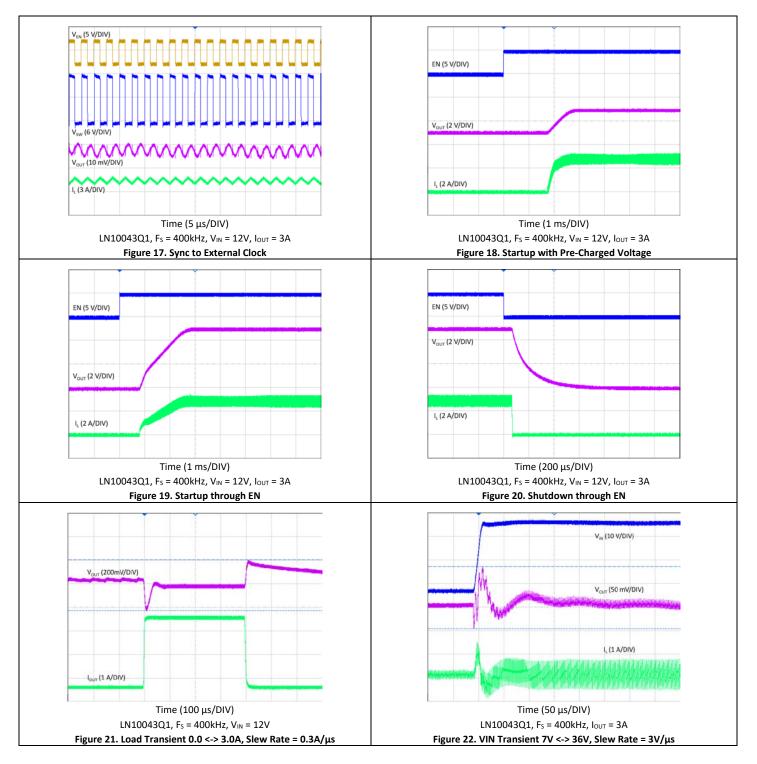

## 7.6 Typical Characteristics

#### 7.6.1 Characteristics Over Temperature

Unless otherwise stated, the test conditions are the same as Chapter 7.5. T<sub>J</sub> = -40°C 到 150°C。

#### 7.6.2 Typical Characteristics

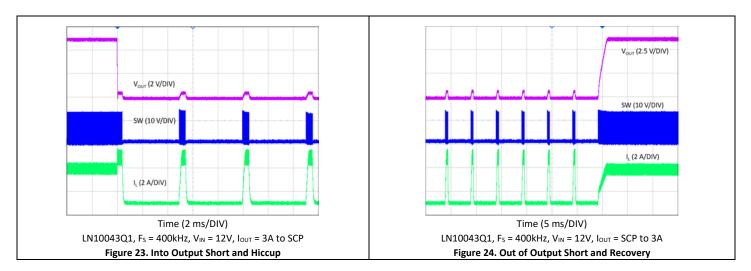

#### 7.6.3 Typical Waveforms

# . EN LEN Technology LTD.

# **Typical Waveforms (Continued)**

# LEN Technology LTD.

# Typical Waveforms (Continued)

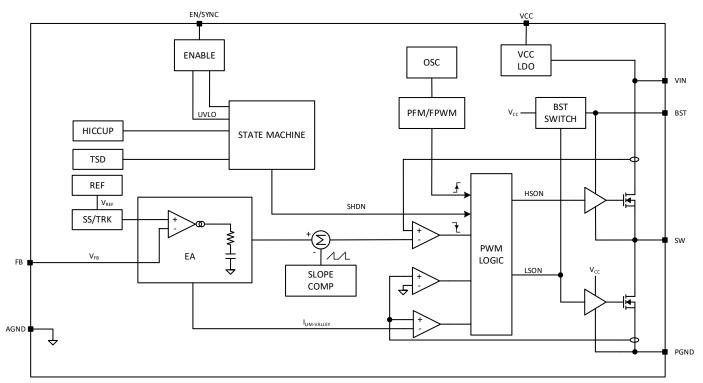

## 8 FUNCTIONAL DESCRIPTION

#### 8.1 Overview

The LN10X43Q1 is a high efficiency, compact, synchronous step-down DC-DC converter employing a constant frequency, peak current mode control architecture with internal compensation. It operates from an input voltage from 3.5V to 36V, provides an adjustable output voltage from 1V to V<sub>IN</sub>. LN10X43Q1 can deliver up to 3.0A.

The LN10X43Q1 has three frequency options: 400kHz, 1MHz and 2.1MHz, or synchronization with an external clock range from 200kHz to 2.1MHz. With a low minimum on-time, it enables a very compact solution with small inductor and capacitor size and offers constant-frequency operation with very high step-down ratio. In addition, the LN10X43Q1 achieves the lowest possible dropout voltage with 100% maximum duty cycle operation. During light load operation, LN10043Q1, LN10243Q1 and LN10443Q1 operate at DCM and PFM to maximize efficiency. LN10143Q1, LN10343Q1 and LN10543Q1 are forced to operate at CCM mode even under zero load.

The LN10X43Q1 also offers a plural of features include programmable output voltage, internal soft start, cycle-by-cycle peak and valley current limit, output short circuit protection with hiccup mode, over temperature shutdown and recovery, and adjustable system UVLO.

The LN10X43Q1S offers a spread spectrum feature to optimize EMI performance. Emissions at the operating frequency and its sub-harmonics are mitigated by spreading the single-point operating frequency over an extended range.

# 8.2 Funtional Diagram

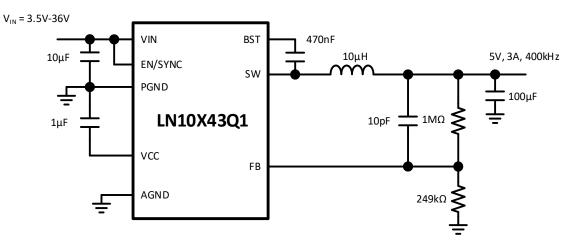

# 8.3 Application Diagram with Full Features

#### 8.4 Funtional Description

#### 8.4.1 Voltage Regulation Loop and FB pin

The LN10X43Q1 employs a peak current mode control to regulate the output voltage. For highly efficient operation cross the whole load range. The LN10043Q1, LN10243Q1 and LN10443Q1 utilizes Discontinuous Conduction Mode (DCM) and Pulse Frequency Modulation (PFM) at light load.

To adjust the output voltage, connect a voltage divider between  $V_{OUT}$  and GND, and connect the center of the divider to FB pin. The steady state  $V_{FB}$  is typically 1V. The output voltage can be derived from:

$$V_{OUT} = (1 + \frac{R_{FBT}}{R_{FBB}}) \times V_{FB}$$

Based on the output voltage requirements, the above equation can be re-written as:

$$R_{FBB} = \frac{V_{FB}}{V_{OUT} - V_{FB}} \times R_{FBT}$$

In general,  $R_{FBT} < 1M\Omega$  is recommended. The tolerance of the divider resistance should be less than 1%, and the temperature coefficients should be less than 100ppm.

The LN10X43Q1 uses an internal compensation scheme to stabilize the control loop, an external RC lead compensation network can be connected between VOUT and FB to improve transient response. An external lead compensation can be achieved by adding a capacitor in parallel with the upper leg resistor of the voltage divider between V<sub>OUT</sub> and FB pins.

The zero frequency of the external lead compensator is at:

$$f_z = \frac{1}{2\pi \times R_{FBT} \times C_{LEAD}}$$

While the pole frequency of the external lead compensator is at:

$$f_{p} = \frac{1}{2\pi \times (R_{FBT} / / R_{FBB}) \times C_{LEAD}}$$

The added external lead compensator can increase the loop gain by  $(1 + \frac{R_{FBT}}{R_{FBR}})$ .

#### 8.4.2 Internal V<sub>cc</sub> Regulators, VCC Pin

$V_{CC}$  powers the internal control circuits and the gate drivers for the internal power MOSFETs. VCC must be decoupled to PGND with a 1 -4.7 $\mu$ F ceramic capacitor.

#### 8.4.3 V<sub>IN</sub> UVLO and EN/SYNC Pin

An accurate threshold is placed at  $EN_{VOUT-ON}$ , when EN rises above this threshold, it turns on the switching regulator. This accurate threshold serves to provide an accurate system  $V_{IN}$  UVLO level. In the application, an enable divider can be added between  $V_{IN}$  and GND. The switching regulator can thus be turned on and off at programmable precise input voltages. The VIN UVLO threshold can be determined by:

$$V_{IN-RISING} = (1 + \frac{R_{ENT}}{R_{ENB}}) \times EN_{VOUT-ON}$$

#### 8.4.4 Synchronization to External Clock and EN/SYNC Pin

LN10X43Q1 is capable of being synchronized to an external clock between 200kHz to 2.1MHz. Connect the external clock signal to EN/SYNC pin.

#### 8.4.5 Over-Current Protection

#### 8.4.5.1 Peak Current Protection

Peak current protection is a cycle-by-cycle protection inherited from the peak current mode control. The peak current command is clamped to the Peak Current Limit Threshold.

#### 8.4.5.2 Valley Current Protection

During low side conduction, the low side power MOSFET current is sensed and compared to valley current threshold. When low side current is higher than the valley current threshold, high side power MOSFET is not allowed to turn on for the next cycle.

#### 8.4.5.3 Hiccup Mode

When low side current is higher than the valley current threshold for 32 cycles, it shuts down the switching regulator. The switching regulator automatically turns back on after 5ms if EN is high. When the switching regulator turns back on, the regulator goes through the soft start process.

#### 8.4.6 Thermal Shutdown and Auto-Recovery

When the junction temperature exceeds 170°C, LN10X43Q1 shuts down the switching regulator to reduce thermal dissipation. It automatically restarts the switching regulator after junction temperature drops back below 160 °C. The VCC LDO regulators remain operational during over-temperature event.

#### 8.4.7 Bootstrap Voltage, BST and SW Pin

The internal gate driver for the high side Power MOSFET uses a bootstrapped supply from an external capacitor  $C_{BST}$  connected between BST pin and SW. The voltage on  $C_{BST}$  is charged from  $V_{CC}$  through an internal switch when the low side power MOSFET conducts.

#### 8.4.8 Low Drop-Out

When input voltage is close to the output target voltage, LN10X43Q1 enters Low Drop-Out mode. The high-side MOSFET can be turned on for more than a switching period to maintain the output voltage regulation. When the input voltage is lower than the target voltage, the high-side power MOSFET is turned on for maximum allowable on time:  $t_{REFRESH-PER}$ . The low-side power MOSFET turns on briefly for  $t_{REFRESH-PUL}$  to refresh the charge on  $C_{BST}$ .

#### 9 APPLICATION INFORMATON

#### 9.1 Typical Applications

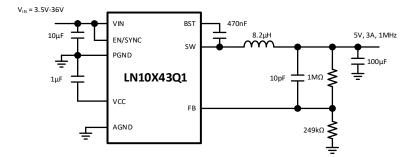

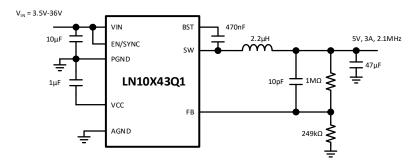

Figure 23. LN10X43Q1, 400kHz, 5V, 3A Typical Application Diagram

Figure 24. LN10X43Q1, 1MHz, 5V, 3A Typical Application Diagram

Figure 25. LN10X43Q1, 2.1MHz, 5V, 3A Typical Application Diagram

# 10 LAYOUT

#### 10.1 Layout Guidelines

The performance of any switching converter depends as much upon the layout of the PCB as the component selection. The LN10X43Q1 is designed to meet the optimization requirements of PCB layout in the pin assignment. For example, VIN and PGND pins are adjacent to each other, which is convenient for placing VIN bypass capacitors.

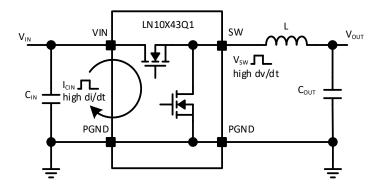

Radiated EMI is generated by the high di/dt components in pulsing currents in switching converters. The larger area covered by the path of a pulsing current; the more electromagnetic emission is generated. As shown in the figure below, this part of the current flows from the VIN side of the input capacitors to high side switch, to the low side switch, and then returns to the ground of the input capacitors.

The key to minimize radiated EMI is to minimize the area of this pulsing current path, thus, placing high frequency ceramic bypass capacitor(s) as close as possible to the VIN and PGND pins is necessary.

In addition, high dv/dt occurs on SW node during switching, so the trace between SW pin and inductor should be as short as possible, and just wide enough to carry the load current without excessive heating. Short and thick traces are highly recommended to minimize parasitic resistance. Besides, sensitive signal lines should be kept away from SW traces.

The following guidelines will help users design a PCB with the best power conversion performance, thermal performance, and minimized generation of unwanted EMI.

1. Place high frequency ceramic bypass  $C_{IN}$  as close as possible to the LN10X43Q1 VIN and PGND pins; a ceramic capacitor in small package (such as 0603) is still needed even if multiple input capacitors are implemented;

2. The high-current loop consisting of VIN, SW, VOUT and GND should be as compact as possible;

3. The bypass capacitors of VCC should be arranged close to the pins, and return to the PGND pin with the shortest connection;

4. It is recommended to use a four-layer board with a top and bottom layer of 2oz copper, and a complete ground plane on middle layer. Use a minimum 2 by 4 arrays of 0.2-millimeter thermal vias to connect the thermal pad of LN10X43Q1 to the system ground plane for heat sinking;

5. The SW and BST nodes contains a lot of high-frequency noise, so

the connection of the pins should be as short as possible, meanwhile, there should be sufficient width to conduct the current;

6. Sensitive analog signals, such as FB, need to be far away from the noisy nodes, ground plane can be used as a shielding layer while routing these sensitive signals;

7. The feedback resistance of the FB connection must be located as close to the pin as possible, If  $V_{OUT}$  accuracy at the load is important, make sure  $V_{OUT}$  sense is made at the load;

8. For the peripheral components connected to FB and EN pins, a single point ground connection to the plane is recommended.

## **11 PACKAGE INFORMATION**

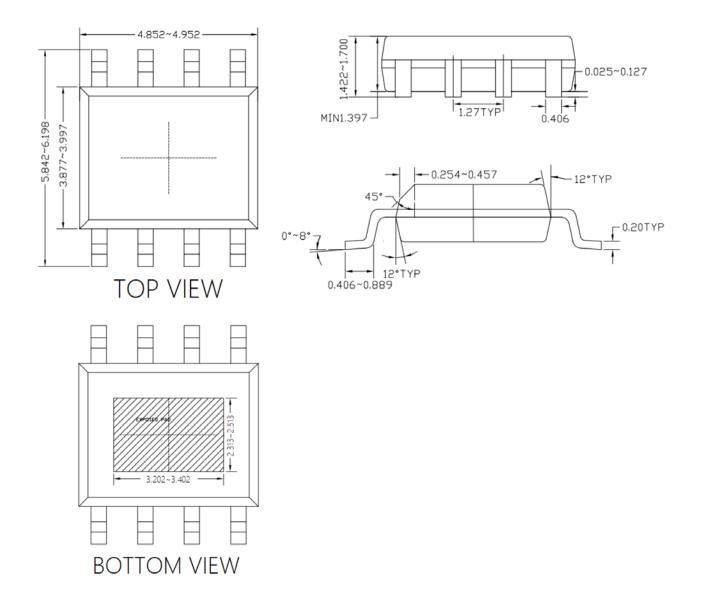

#### 11.1 Package Outline

Notes:

- 1. Both package length and width do not include mold flash.

- 2. Controlling dimension: mm

- 3. Reference JEDEC MS-013, MS-012

- 4. The size label of length and width in the drawing belong to the bottom size of the package.

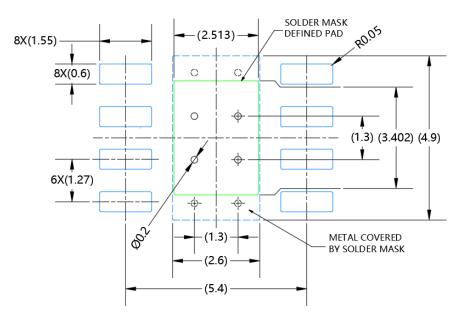

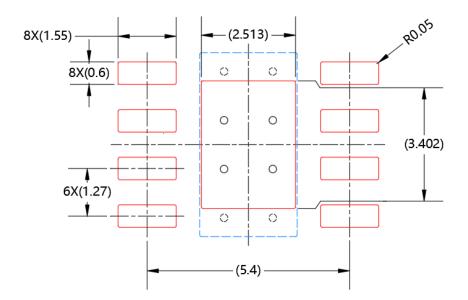

# **11.2** Footprint Example

LAND PATTERN EXAMPLE EXPOSED METAL SHOWN

SOLDER PASTE EXAMPLE BASED ON 0.125 mm THICK STENCIL

#### **IMPORTANT NOTICE AND DISCLAIMERS**

The technical materials, reliability data, product specifications, and related product evaluation boards provided by LEN Technology Ltd. are on an "as is" basis. LEN Technology Ltd. is not responsible for any errors that may occur in these resources. LEN Technology Ltd. disclaims all expressed and implied warranties, including any implied warranties that the intellectual property rights of third parties will not be infringed.

These resources from LEN Technology Ltd. are provided only to those who have experience in developing electronic products. You will be solely responsible for selecting appropriate products from LEN Technology Ltd., and for verifying and testing your design to meet the standards of your application, as well as for any other safety and security requirements.

The resources provided by LEN Technology Ltd. are subject to change without notice. LEN Technology Ltd. Only grants you the rights for developing applications with the products of LEN Technology Ltd. described in these resources. Reproduction and display of these resources is prohibited. LEN Technology Ltd. does not grant any other intellectual property rights owned by LEN Technology Ltd. or any third-party licensed intellectual property. LEN Technology Ltd. does not assume any loss, cost and liabilities for the use of these resources.

## **ENVIRONMENTAL DECLARATION**

This product complies with the requirements of RoHS and REACH. In accordance with relevant Chinese regulations and standards, it does not contain toxic or harmful substances or elements.