# PE4 series

## Enterprise-grade PCIe SSD

## **Specifications**

#### Capacity

U.2: 960 GB~7680 GB

E1.S: 960 GB~7680 GB

M.2 2280: 960 GB~7680 GB

M.2 2242: 240 GB~1920 GB

M.2 2230: 240 GB~960 GB

#### Components

Controller: Marvell 88SS1321 Flash: 1.2GHz 3D TLC

DRAM: DDR4

#### Compliance

PCIe Gen4x4/ Gen4x2/ Gen3x4

Surprise insertion / surprise removal (SISR) and hotplug capable (U.2/E1.S support)

#### Performance (up to)<sup>1</sup>

Sequential read: 3.500 MB/s Sequential write: 3.000 MB/s Random 4K read: 400,000 IOPS Random 4K write: 50,000 IOPS

#### **Power management**

Auto idle

PCIe link power management

Temperature monitoring and throttling

#### Security

**NVM Format**

Support SED (TCG/AES) (Optional)

Advanced LDPC error correction

Global static and dynamic wear leveling

Hardware Power Loss Protection (PLP) (For U.2 & E1.S form factor, customized for M.2 2280 and support to 3840GB)

<1 sector per 10<sup>17</sup> bits read UBER:

MTBF: 2.0 million hours

#### Physical insertion cycles

Nominal: 2000 (Optional: 5000)

#### Endurance<sup>2</sup>

0.6 DWPD @5 Years (Sequential workload: 1.5 DWPD @5 Years)

240GB: 250TB / 480GB: 500TB

960GB: 1000TB / 1920GB: 2000TB

3840GB: 4000TB / 7680GB: 8000TB

#### Data retention

JESD218A-compliant

#### Compatibility

Windows 11/10/8.1/7

Windows Server 2016/2012 R2/2012

CentOS, Fedora, FreeBSD, openSUSE, Red Hat, Ubuntu, VMware ESXi, Citrix, KVM

#### Mechanical form factor

100.5 mm x 69.85 mm x 7 mm U.2: M.2 2280: 80 mm x 22 mm x 3.5 mm M.2 2242: 42 mm x 22 mm x 3.5 mm M.2 2230: 30 mm x 22 mm x 2.15 mm E1.S: 111.49 mm x 31.5 mm x 5.9 mm

#### Power consumption (TYP)

Max: <12.0 W Active: <7.0 W <1.0 W Idle:

#### Environment

Operating temperature: 0-70 °C Storage temperature: -40-85 °C

#### **Shock & vibration**

Operating: 50 G (11 ms duration, half sine wave)

Non-operating: 1500 G (0.5 ms duration, half sine wave)

Vibration: 10 G (peak, 10-2000 Hz)

#### Warranty

5-year limited warranty<sup>3</sup>

#### **Specification notes:**

- 1. Performance claims

- a. Actual performance may vary based on the hardware, software, and overall system configuration.

- b. Sequential performance is measured with 128 KB transfer size, QD 32 and 4 KB alignment with Iometer.

- c. Random performance is sustained performance measured with 4K/8K transfer size, QD 32 and 4 KB alignment with Iometer.

- d. Performance test platform: CPU: Intel Core i7 4770K; motherboard: ASUS Z87-DELUXE; chipset: Intel Z87 Express; OS: Windows 8.1 Pro x64.

- 2. Endurance claims

- DWPD stands for Drive Writes Per Day. TBW = DWPD \* capacity \* warranty \* 365 / 1000.

- b. Access patterns used for random workload during endurance testing is compliant with the JESD219 standard.

- 3. Limited warranty details: please refer to limited warranty policy and warranty terms.

## **Table of Contents**

| Specifications                        |    |

|---------------------------------------|----|

| Product datasheet                     | 4  |

| 1. Order information                  |    |

| 2. Part number decoder                | 5  |

| 3. Product overview                   | ε  |

| 3.1 PE4 series                        | ε  |

| 3.2 Customization and tuning services | ε  |

| 4. Detailed specifications            | 7  |

| 4.1 Capacity                          | 7  |

| 4.2 Performance                       | 7  |

| 4.3 Environment specification         | 8  |

| 4.4 Power consumption                 | 8  |

| 4.5 Reliability                       | 8  |

| 5. Physical dimension diagram         | 9  |

| 5.1 U.2 board                         | 9  |

| 5.2 PCle M.2 2280                     | 10 |

| 5.3 PCIe M.2 2242                     | 11 |

| 5.4 PCle M.2 2230                     | 12 |

| 5.5 PCle E1.S without heat sink       | 13 |

| 5.6 PCle E1.S with heat sink          | 14 |

| 6. Pin Assignment                     | 15 |

| 6.1 U.2 connector                     |    |

| 6.2 PCIe M.2 2280/2242/2230 connector |    |

| 6.3 E1.S connector                    | 19 |

| 7. Compliance                         | 21 |

| 8. PCI and NVM Express Registers      | 22 |

| 8.1 PCI Register                      |    |

| 8.2 NVM Express Register              |    |

| 9. Supported NVMe commands            | 54 |

| 9.1 Admin Commands                    | 54 |

| 9.2 NVM Commands                      |    |

| 9.3 Log Pages                         | 69 |

| 9.4 NVMe Features                     |    |

| 10. S.M.A.R.T. support                | 70 |

| 10.1 Overview of S.M.A.R.T. support   |    |

| 10.2 S.M.A.R.T. health information    | 70 |

| Legal information                     | 72 |

| Limited Warranty Policy               | 72 |

| Warranty Terms                        | 72 |

| Disclaimer of liability               | 72 |

| Copyright notice                      |    |

| Contact information                   | 73 |

| Revision history                      | 74 |

## Product datasheet

#### 1. Order information

The following table lists the standard part numbers for Exascend PE4 series SSDs. For customization and design service inquiries, including – but not limited to – custom operating temperature, capacity, over-provisioning, endurance, performance, and power, please contact your Exascend account manager or send us an email at <a href="mailto:sales@exascend.com">sales@exascend.com</a>.

Table 1: PE4 series SSD product list

| PART NUMBER   | CAPACITY* | FLASH TYPE | FORM FACTOR |

|---------------|-----------|------------|-------------|

| EXPE4R240GB   | 240GB *   | 3D TLC     | M.2 2230    |

| EXPE4R480GB   | 480GB *   | 3D TLC     | M.2 2230    |

| EXPE4R960GB   | 960GB *   | 3D TLC     | M.2 2230    |

| EXPE4Q240GB   | 240GB *   | 3D TLC     | M.2 2242    |

| EXPE4Q480GB   | 480GB *   | 3D TLC     | M.2 2242    |

| EXPE4Q960GB   | 960GB *   | 3D TLC     | M.2 2242    |

| EXPE4Q1920GB  | 1920GB *  | 3D TLC     | M.2 2242    |

| EXPE4M960GB   | 960GB *   | 3D TLC     | M.2 2280    |

| EXPE4M1920GB  | 1920GB *  | 3D TLC     | M.2 2280    |

| EXPE4M3840GB  | 3840GB *  | 3D TLC     | M.2 2280    |

| EXPE4M7680GB  | 7680GB *  | 3D TLC     | M.2 2280    |

| EXPE4U960GB   | 960GB *   | 3D TLC     | U.2         |

| EXPE4U1920GB  | 1920GB *  | 3D TLC     | U.2         |

| EXPE4U3840GB  | 3840GB *  | 3D TLC     | U.2         |

| EXPE4U7680GB  | 7680GB *  | 3D TLC     | U.2         |

| EXPE4U15360GB | 15360GB * | 3D TLC     | U.2         |

| EXPE4E960GB   | 960GB *   | 3D TLC     | E1.S        |

| EXPE4E1920GB  | 1920GB *  | 3D TLC     | E1.S        |

| EXPE4E3840GB  | 3840GB *  | 3D TLC     | E1.S        |

| EXPE4E7680GB  | 7680GB *  | 3D TLC     | E1.S        |

#### 2. Part number decoder

| 1  | 2   | 3 | 4     | 5 | 6  |

|----|-----|---|-------|---|----|

| EX | PE4 | R | 240GB | - | ** |

- 1. Exascend

- 2. Product series

(SC1/SC3/PC3/PC4/SE1/SE3/PE3/PE4/SI2/SI3/PI3/PE4/PI4)

3. Form factor

(A=2.5"; B=mSATA; M=M.2 2280; P=M.2 2260; Q=M.2 2242; R=M.2 2230; U=U.2; E=E1.S)

- 4. Capacity

- 5. Hyphen

- 6. Identifier (H= extended temp, WP= with PLP)

#### 3. Product overview

#### 3.1 PE4 series

Exascend provides customizable hardware and firmware design, manufacturing, and service of cutting-edge SSD products and advanced storage systems. Our products are designed specifically for high reliability commercial, enterprise data center, and cloud computing applications. By combining world class design R&D, and superior execution in delivery and support capabilities, Exascend strives to provide customers with the best in class product and service, enabling enhanced boot times, faster application load times, reduced power consumption and extended reliability.

PE4 series product supports U.2, E1.S, and M.2 form factors, integrating high speed PCIe Gen 4 x 4 interface with third generation 3D TLC NAND flash memory technology, delivering capacities up to 8TB.

PE4 series products are offered in two product categories with different over-provisioning.

Key product highlights include:

- High I/O and throughput performance

- Next generation LDPC technology secures NAND endurance

- Advanced Flash management and global wear leveling algorithm extending drive life

- · High stability and reliability

- Temperature monitoring and intelligent management

Figure 1: SSD functional logic diagram

#### 3.2 Customization and tuning services

Exascend provides customized hardware and firmware design services, tailoring cutting-edge SSD products for advanced storage systems. Combining world-class R&D and engineering support capabilities, Exascend provides customers with best-in-class products and services, enabling enhanced boot times, faster-loading applications, reduced power consumption, and extended reliability. To learn more about our extended engineering support services, e.g., tailored capacity, over-provisioning, extended operating temperature range, endurance, performance, power, and longevity, please contact your Exascend account manager or send us an email at <a href="mailto:sales@exascend.com">sales@exascend.com</a>.

### 4. Detailed specifications

Exascend PE4 series SSD provides you the ultimate performance and ultra-high reliability over traditional hard disk drive by achieving up to 3,500MB/s for sequential read, 3,000MB/s for sequential write, 500,000 IOPS for random read, 55,000 IOPS for steady state random write.

Exascend PE4 series SSD consists solely of semiconductor devices, it does not contain any mechanical part such as platter (disk), motor and suspension as traditional hard disk drive. Thus, it exhibits superior performance, capacity, reliability, ruggedness, low power, and small form factor profiles that qualified to be the best storage solution for enterprise application with extreme workloads and increased MTBF requirements.

Exascend PE4 SSD uses a single-chip Flash controller to manage multiple NAND Flash memory modules. The controller works with a host system to allow data to be written to and read from the Flash memory modules through a PCIe interface.

#### 4.1 Capacity

Table 2: PE4 logical block address configuration

| PE4 SERIES | UNFORMATTED CAPACITY<br>(TOTAL USER ADDRESSABLE SECTORS IN LBA MODE) |

|------------|----------------------------------------------------------------------|

| 240 GB     | 468,862,128                                                          |

| 480 GB     | 937,703,088                                                          |

| 960 GB     | 1,875,385,008                                                        |

| 1,920 GB   | 3,750,748,848                                                        |

| 3,840 GB   | 7,501,476,528                                                        |

| 7,680 GB   | 15,002,931,888                                                       |

#### Notes:

- The LBA count shown represents total user-accessible storage capacity and will remain the same throughout the drive's lifetime.

- The total usable capacity of the SSD may be less than the total physical capacity because a small portion of the capacity is used for NAND flash management and maintenance purposes.

#### 4.2 Performance

Table 3: Drive performance - PE4 series

|                       | UNIT                                    |         |          |         | 1         | PE4 SERIES |        |        |           |

|-----------------------|-----------------------------------------|---------|----------|---------|-----------|------------|--------|--------|-----------|

| Capacity              | GB                                      | 240GB   | 480GB    | 960GB   | 1920GB    | 3840GB     | 7680GB | 3840GB | 7680GB    |

| Sequential read       | MB/s                                    | 2,000   | 3,200    | 3,200   | 3,200     | 2,800      | 2,200  | 3,500  | 3,500     |

| Sequential write      | MB/s                                    | 450     | 900      | 1,800   | 3,000     | 2,800      | 2,200  | 3,000  | 3,000     |

| Sustained read (4KB)  | IOPS                                    | 60K     | 120K     | 240K    | 400K      | 400K       | 400K   | 400K   | 400K      |

| Sustained write (4KB) | IOPS                                    | 15K     | 15K      | 30K     | 50K       | 50K        | 50K    | 50K    | 50K       |

| DWPD<br>(5 years)     | 0.6 @ JESD218<br>1.5 @ Sequential Write |         |          |         |           |            |        |        |           |

| Form factor           |                                         | M.2 223 | 0 & 2242 | M.2, E1 | I.S & U.2 | M.2        | 2280   | E′     | 1.S & U.2 |

#### Notes:

- Measured with device connected as secondary drive.

- Actual performance may vary based on the hardware, software, and overall system configuration.

- Sequential performance is measured with 128 KB transfer size, QD 32 and 4 KB alignment with lometer.

- Random performance is sustained performance measured with 4K/8K transfer size, QD 32 and 4 KB alignment with Iometer.

- Performance test platform: CPU: Intel Core i7 4770K; motherboard: ASUS Z87-DELUXE; chipset: Intel Z87 Express; OS: Windows 8.1 Pro x64.

#### 4.3 Environment specification

Table 4: Environmental specification table

| PARAMETER                  | VALUE                                      |

|----------------------------|--------------------------------------------|

| Operating temperature      | 0–70 °C                                    |

| Storage temperature        | -40–85 °C                                  |

| Power supply voltage range | U.2 / E1.S: 12.0 V ±10%<br>M.2: 3.3 V ± 5% |

| Humidity (non-condensing)  | 5-95% (Operating)                          |

| Vibration                  | 10 G (peak, 10-2000 Hz)                    |

| Shock (operating)          | 50 G, (11 ms duration, half sine wave)     |

| Shock (non-operating)      | 1500 G, (0.5 ms duration, half sine wave)  |

#### 4.4 Power consumption

Table 5: PE4 series power consumption table

| PARAMETER                 | VALUE | UNIT |

|---------------------------|-------|------|

| Max power (average)       | <12.0 | W    |

| Active power (average)    | <7.0  | W    |

| Idle mode power (average) | <1.0  | W    |

#### 4.5 Reliability

Products in the Exascend PE4 series meet or exceed SSD endurance and data retention requirements as specified in the JESD218 standard. Reliability specifications are listed in the following table.

Table 6: Reliability table

| PARAMETER                                                                                                                                                                                   | VALUE                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Mean Time Between Failures (MTBF) Mean Time Between Failures is a measure of how reliable a hardware product or a component is. The value describes the expected time between two failures. | 2,000,000 hours                                                                                     |

| Uncorrectable Bit Error Rate (UBER) A metric for the rate of occurrence of data errors, equal to the number of data errors per bits read.                                                   | <1 sector per 10 <sup>17</sup>                                                                      |

| Endurance Rating (TBW) TBW stands for total bytes written whose access pattern is compliant with JESD218 standard.                                                                          | 240GB: 250TB<br>480GB: 500TB<br>960GB: 1000TB<br>1920GB: 2000TB<br>3840GB: 4000TB<br>7680GB: 8000TB |

## 5. Physical dimension diagram

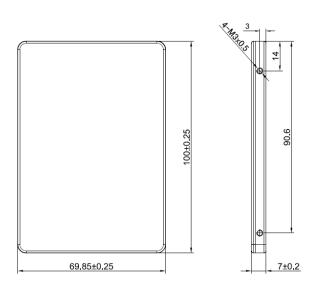

#### 5.1 U.2 board

Figure 2: U.2 physical dimension diagram

GENERAL TOLERANCE IS ±0.15mm DIMENSION UNIT: mm

Table 7: Physical dimensions for U.2

| PHYSICAL DIMENSIONS | VALUE | UNIT |

|---------------------|-------|------|

| Length              | 100   | mm   |

| Width               | 69.85 | mm   |

| Thickness           | 7     | mm   |

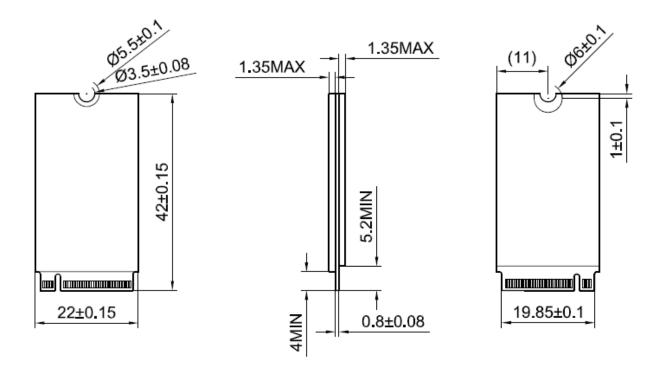

#### 5.2 PCIe M.2 2280

Figure 3: M.2 2280 physical dimension diagram

Table 8: Physical dimensions for M.2 2280

| PHYSICAL DIMENSIONS | VALUE | UNIT |

|---------------------|-------|------|

| Length              | 80    | mm   |

| Width               | 22    | mm   |

| Thickness           | 3.5   | mm   |

#### 5.3 PCIe M.2 2242

Figure 4: M.2 2242 physical dimension diagram

Table 9: Physical dimensions for M.2 2242

| PHYSICAL DIMENSIONS | VALUE | UNIT |

|---------------------|-------|------|

| Length              | 42    | mm   |

| Width               | 22    | mm   |

| Thickness           | 3.5   | mm   |

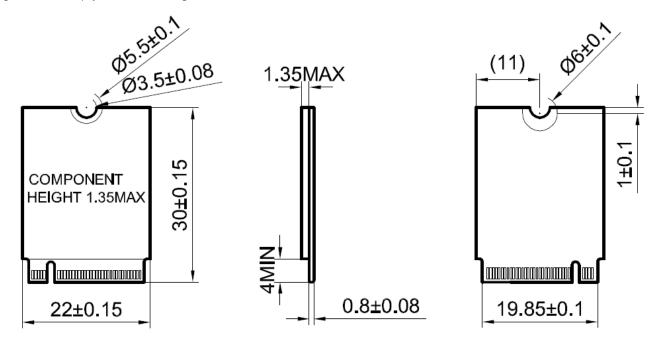

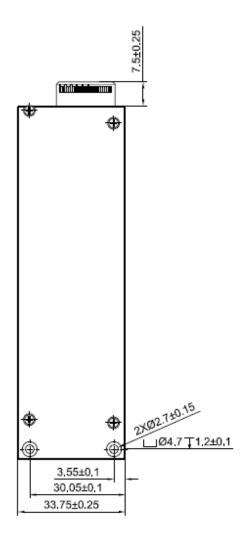

#### 5.4 PCIe M.2 2230

Figure 5: M.2 2230 physical dimension diagram

Table 10: Physical dimensions for M.2 2230

| PHYSICAL DIMENSIONS | VALUE | UNIT |

|---------------------|-------|------|

| Length              | 30    | mm   |

| Width               | 22    | mm   |

| Thickness           | 2.15  | mm   |

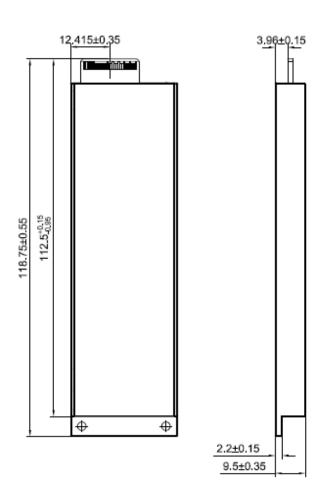

#### 5.5 PCle E1.S without heat sink

Figure 6: E1.S physical dimension diagram

Table 11: Physical dimensions for E1.S

| PHYSICAL DIMENSIONS | VALUE  | UNIT |

|---------------------|--------|------|

| Length              | 111.49 | mm   |

| Width               | 31.5   | mm   |

| Thickness           | 5.9    | mm   |

#### 5.6 PCle E1.S with heat sink

Figure 7: E1.S physical dimension diagram

Table 12: Physical dimensions for E1.S

| PHYSICAL DIMENSIONS | VALUE  | UNIT |

|---------------------|--------|------|

| Length              | 118.75 | mm   |

| Width               | 33.75  | mm   |

| Thickness           | 9.5    | mm   |

## 6. Pin Assignment

#### 6.1 U.2 connector

Table 13: U.2 connector signal name, power pin assignment, and description

| PIN NAME   | ne, power pin assignment, and description SIGNAL NAME | DESCRIPTION                                   |

|------------|-------------------------------------------------------|-----------------------------------------------|

| S1         | GND                                                   | Ground                                        |

| <b>S2</b>  | Not used                                              | Not used                                      |

| <b>S</b> 3 | Not used                                              | Not used                                      |

| S4         | GND                                                   | Ground                                        |

| <b>S</b> 5 | Not used                                              | Not used                                      |

| S6         | Not used                                              | Not used                                      |

| <b>S</b> 7 | GND                                                   | Ground                                        |

| E1         | Not used                                              | Not used                                      |

| E2         | Not used                                              | Not used                                      |

| E3         | 3.3Vaux                                               | 3.3 V Power                                   |

| E4         | Not used                                              | Not used                                      |

| E5         | PERST0#                                               | Fundamental reset port 0                      |

| E6         | Reserved                                              | Reserved                                      |

| P1         | Not used                                              | Not used (SATA/SAS)                           |

| P2         | Not used                                              | Not used (SATA/SAS)                           |

| P3         | CLKREQ                                                | CLKREQ                                        |

| P4         | IfDet_N                                               | Interface detection (drive type)              |

| P5         | GND                                                   | Ground                                        |

| P6         | GND                                                   | Ground                                        |

| P7         | Not used                                              | Not used (SATA/SAS)                           |

| P8         | Not used                                              | Not used (SATA/SAS)                           |

| P9         | Not used                                              | Not used (SATA/SAS)                           |

| P10        | PRSNT_N                                               | Presence detection (also used for drive type) |

| P11        | Activity                                              | Activity signal from the drive                |

| P12        | Hot-Plug                                              | Ground                                        |

| P13        | +12V_pre                                              | 12V Power                                     |

| P14        | +12V                                                  | 12 V Power                                    |

| P15        | +12V                                                  | 12 V Power                                    |

| <b>E</b> 7 | REFCLK0+                                              | Reference clock port 0 +                      |

| E8         | REFCLK0-                                              | Reference clock port 0 -                      |

| E9         | GND                                                   | Ground                                        |

| E10        | PERp0                                                 | + Receive differential pair, channel 0        |

| E11        | PERn0                                                 | - Receive differential pair, channel 0        |

| E12        | GND                                                   | Ground                                        |

| E13        | PETn0                                                 | - Transmit differential pair, channel 0       |

| E14 | PETp0        | + Transmit differential pair, channel 0 |

|-----|--------------|-----------------------------------------|

| E15 | GND          | Ground                                  |

| E16 | Reserved     | Reserved                                |

| S8  | GND          | Ground                                  |

| S9  | Not used     | Not used (SATA/SAS)                     |

| S10 | Not used     | Not used (SATA/SAS)                     |

| S11 | GND          | Ground                                  |

| S12 | Not used     | Not used (SATA/SAS)                     |

| S13 | Not used     | Not used (SATA/SAS)                     |

| S14 | GND          | Ground                                  |

| S15 | Reserved     | Reserved                                |

| S16 | GND          | Ground                                  |

| S17 | PERp1        | + Receive differential pair, channel 1  |

| S18 | PERn1        | - Receive differential pair, channel 1  |

| S19 | GND          | Ground                                  |

| S20 | PETn1        | - Transmit differential pair, channel 1 |

| S21 | PETp1        | + Transmit differential pair, channel 1 |

| S22 | GND          | Ground                                  |

| S23 | PERp2        | + Receive differential pair, channel 2  |

| S24 | PERn2        | - Receive differential pair, channel 2  |

| S25 | GND          | Ground                                  |

| S26 | PETn2        | - Transmit differential pair, channel 2 |

| S27 | PETp2        | + Transmit differential pair, channel 2 |

| S28 | GND          | Ground                                  |

| E17 | PERp3        | + Receive differential pair, channel 3  |

| E18 | PERn3        | - Receive differential pair, channel 3  |

| E19 | GND          | Ground                                  |

| E20 | PETn3        | - Transmit differential pair, channel 3 |

| E21 | PETp3        | + Transmit differential pair, channel 3 |

| E22 | GND          | Ground                                  |

| E23 | SMCLK        | SMBus clock                             |

| E24 | SMDAT        | SMBus data                              |

| E25 | DualPortEn N | Dual port enable                        |

#### 6.2 PCIe M.2 2280/2242/2230 connector

Table 14: M.2 2280/2242/2230 connector signal name, power pin assignment, and description

| PIN NAME | nector signal name, power pin assignment, SIGNAL NAME | DESCRIPTION            |

|----------|-------------------------------------------------------|------------------------|

| 1        | GND                                                   | Ground                 |

| 2        | 3.3V                                                  | 3.3V Power             |

| 3        | GND                                                   | Ground                 |

| 4        | 3.3V                                                  | 3.3V Power             |

| 5        | PCIe 3 TXn                                            | PCIe Lane 3 TX-        |

| 6        | Reserved                                              | Reserved               |

| 7        | PCIe 3 TXp                                            | PCIe Lane 3 TX+        |

| 8        | Reserved                                              | Reserved               |

| 9        | GND                                                   | Ground                 |

| 10       | DAS                                                   | Device Activity Signal |

| 11       | PCIe 3 RXn                                            | PCIe Lane 3 RX-        |

| 12       | 3.3V                                                  | 3.3V Power             |

| 13       | PCIe 3 RXp                                            | PCIe Lane 3 RX+        |

| 14       | 3.3V                                                  | 3.3V Power             |

| 15       | GND                                                   | Ground                 |

| 16       | 3.3V                                                  | 3.3V Power             |

| 17       | PCIe 2 TXn                                            | PCIe Lane 2 TX-        |

| 18       | 3.3V                                                  | 3.3V Power             |

| 19       | PCIe 2 TXp                                            | PCIe Lane 2 TX+        |

| 20       | NC                                                    | No Connection          |

| 21       | GND                                                   | Ground                 |

| 22       | UART RX                                               | Manufacturing Use      |

| 23       | PCIe 2 RXn                                            | PCIe Lane 2 RX-        |

| 24       | NC                                                    | No Connection          |

| 25       | PCIe 2 RXp                                            | PCIe Lane 2 RX+        |

| 26       | Reserved                                              | Reserved               |

| 27       | GND                                                   | Ground                 |

| 28       | Reserved                                              | Reserved               |

| 29       | PCIe 1 TXn                                            | PCIe Lane 1 TX-        |

| 30       | Reserved                                              | Reserved               |

| 31       | PCIe 1 TXp                                            | PCIe Lane 1 TX+        |

| 32       | UART TX                                               | Manufacturing Use      |

| 33       | GND                                                   | Ground                 |

| 34       | Reserved                                              | Reserved               |

| 35       | PCIe 1 RXn                                            | PCIe Lane 1 RX-        |

| 36       | Reserved                                              | Reserved               |

| 37       | PCIe 1 RXp                                            | PCIe Lane 1 RX+        |

| 38 | Reserved        | Reserved            |

|----|-----------------|---------------------|

| 39 | GND             | Ground              |

| 40 | SCL             | SMBus_SCL           |

| 41 | PCIe 0 TXn      | PCIe Lane 0 TX-     |

| 42 | SDA             | SMBus_SDA           |

| 43 | PCIe 0 TXp      | PCIe Lane 0 TX+     |

| 44 | NC              | No Connection       |

| 45 | GND             | Ground              |

| 46 | NC              | No Connection       |

| 47 | PCIe 0 RXn      | PCIe Lane 0 RX-     |

| 48 | NC              | No Connection       |

| 49 | PCIe 0 RXp      | PCIe Lane 0 RX+     |

| 50 | PERST           | PCIe Reset          |

| 51 | GND             | Ground              |

| 52 | CLKREQ          | PCIe Clock Request  |

| 53 | Ref CLKN        | PCIe Reference clk- |

| 54 | NC              | No Connection       |

| 55 | Ref CLKP        | PCIe Reference clk+ |

| 56 | NC              | No Connection       |

| 57 | GND             | Ground              |

| 58 | NC              | No Connection       |

| 59 | PCIe Module Key | PCIe Module Key     |

| 60 | PCIe Module Key | PCIe Module Key     |

| 61 | PCIe Module Key | PCIe Module Key     |

| 62 | PCIe Module Key | PCIe Module Key     |

| 63 | PCIe Module Key | PCIe Module Key     |

| 64 | PCIe Module Key | PCIe Module Key     |

| 65 | PCIe Module Key | PCIe Module Key     |

| 66 | PCIe Module Key | PCIe Module Key     |

| 67 | NC              | No Connection       |

| 68 | NC              | No Connection       |

| 69 | NC              | No Connection       |

| 70 | 3.3V            | 3.3V Power          |

| 71 | GND             | Ground              |

| 72 | 3.3V            | 3.3V Power          |

| 73 | GND             | Ground              |

| 74 | 3.3V            | 3.3V Power          |

| 75 | GND             | Ground              |

#### 6.3 E1.S connector

Table 15: E1.S connector signal name, power pin assignment, and description

| PIN NAME | ame, power pin assignment, and description  1st mate | SIGNAL NAME     |

|----------|------------------------------------------------------|-----------------|

| A1       | 1st mate                                             | GND             |

| A2       | 1st mate                                             | GND             |

| A3       | 1st mate                                             | GND             |

| A4       | 1st mate                                             | GND             |

| A5       | 1st mate                                             | GND             |

| A6       | 2nd mate                                             | GND             |

| A7       | 2nd mate                                             | SMBCLK          |

| A8       | 2nd mate                                             | SMBDAT          |

| A9       | 2nd mate                                             | SMBRST#         |

| A10      | 2nd mate                                             | LED#/ACTIVITY   |

| A11      | 2nd mate                                             | PERST1#/CLKREQ# |

| A12      | 1st mate                                             | PRSNTO#         |

| A13      | 2nd mate                                             | GND             |

| A14      | 2nd mate                                             | REFCLKn1        |

| A15      | 1st mate                                             | REFCLKp1        |

| A16      | 2nd mate                                             | GND             |

| A17      | 2nd mate                                             | PERn0           |

| A18      | 1st mate                                             | PERp0           |

| A19      | 2nd mate                                             | GND             |

| A20      | 2nd mate                                             | PERn1           |

| A21      | 1st mate                                             | PERp1           |

| A22      | 2nd mate                                             | GND             |

| A23      | 2nd mate                                             | PERn2           |

| A24      | 1st mate                                             | PERp2           |

| A25      | 2nd mate                                             | GND             |

| A26      | 2nd mate                                             | PERn3           |

| A27      | 1st mate                                             | PERp3           |

| A28      | 1st mate                                             | GND             |

| B1       | 2nd mate                                             | 12V             |

| B2       | 2nd mate                                             | 12V             |

| B3       | 2nd mate                                             | 12V             |

| B4       | 2nd mate                                             | 12V             |

| B5       | 2nd mate                                             | 12V             |

| B6       | 2nd mate                                             | 12V             |

| B7       | 2nd mate                                             | MFG             |

| B8       | 2nd mate                                             | RFU             |

| В9       | 2nd mate                                             | DUALPORTEN#     |

| B10 | 2nd mate | PERSTO#  |

|-----|----------|----------|

| B11 | 2nd mate | 3.3 VAux |

| B12 | 2nd mate | PWRDIS   |

| B13 | 1st mate | GND      |

| B14 | 2nd mate | REFCLKn0 |

| B15 | 2nd mate | REFCLKp0 |

| B16 | 1st mate | GND      |

| B17 | 2nd mate | PETn0    |

| B18 | 2nd mate | PETp0    |

| B19 | 1st mate | GND      |

| B20 | 2nd mate | PETn1    |

| B21 | 2nd mate | PETp1    |

| B22 | 1st mate | GND      |

| B23 | 2nd mate | PETn2    |

| B24 | 2nd mate | PETp2    |

| B25 | 1st mate | GND      |

| B26 | 2nd mate | PETn3    |

| B27 | 2nd mate | PETp3    |

| B28 | 1st mate | GND      |

## 7. Compliance

Exascend PE4 series SSD complies with the following specifications:

- FCC

- CE

- RoHS

## 8. PCI and NVM Express Registers

#### 8.1 PCI Register

#### 8.1.1 PCI Register Summary

Table 16: PCI Register Summary

| Start Address | End Address | Name                                             | Туре           |

|---------------|-------------|--------------------------------------------------|----------------|

| 00h           | 3Fh         | PCI Header                                       | PCI Capability |

| 40h           | 47h         | PCI Power Management Capability                  | PCI Capability |

| 50h           | 67h         | MSI Capability                                   | PCI Capability |

| 70h           | A3h         | PCI Express Capability                           | PCI Capability |

| B0h           | BBh         | MSI-X Capability                                 | PCI Capability |

| 100h          | 12Bh        | Advanced Error Reporting Capability              | PCI Capability |

| 148h          | 153h        | Device Serial No Capability                      | PCI Capability |

| 158h          | 167h        | Power Budgeting Capability                       | PCI Capability |

| 168h          | 16Fh        | Alternative Routing-ID Interpretation Capability | PCI Capability |

| 178h          | 18Bh        | Secondary PCI Express Header                     | PCI Capability |

| 198h          | 1A7h        | Physical LAYER 16.0 GT/s Extended Capability     | PCI Capability |

| 1BCh          | 1C7h        | Margining Extended Capability                    | PCI Capability |

| 224h          | 22Bh        | Latency Tolerance Reporting (LTR)                | PCI Capability |

| 22Ch          | 23Bh        | L1 Substates Capability Register                 | PCI Capability |

### 8.1.2 PCI Header Register

Table 17: PCI Header Register Summary

| Start Address | End Address | Symbol       | Description                                 |

|---------------|-------------|--------------|---------------------------------------------|

| 00h           | 03h         | ID           | Identifiers                                 |

| 04h           | 05h         | CMD          | Command Register                            |

| 06h           | 07h         | STS          | Device Status                               |

| 08h           | 08h         | RID          | Revision ID                                 |

| 09h           | 0Bh         | CC           | Class Codes                                 |

| 0Ch           | 0Ch         | CLS          | Cache Line Size                             |

| 0Dh           | 0Dh         | MLT          | Master Latency Timer                        |

| 0Eh           | 0Eh         | HTYPE        | Header Type                                 |

| 0Fh           | 0Fh         | BIST         | Built in Self Test                          |

| 10h           | 13h         | MLBAR (BAR0) | Memory Register Base Address (lower 32-bit) |

| 14h | 17h | MUBAR (BAR1) | Memory Register Base Address (upper 32-bit) |

|-----|-----|--------------|---------------------------------------------|

| 18h | 1Bh | IDBAR (BAR2) | Index/Data Pair Register Base Address       |

| 1Ch | 1Fh | BAR3         | Reserved                                    |

| 20h | 23h | BAR4         | Reserved                                    |

| 24h | 27h | BAR5         | Reserved                                    |

| 28h | 2Bh | CCPTR        | CardBus CIS Pointer                         |

| 2Ch | 2Fh | SS           | Subsystem Identifiers                       |

| 30h | 33h | EROM         | Expansion ROM Base Address                  |

| 34h | 34h | CAP          | Capabilities Pointer                        |

| 35h | 3Bh | RO           | Reserved                                    |

| 3Ch | 3Dh | INTR         | Interrupt Information                       |

| 3Eh | 3Eh | MGNT         | Minimum Grant                               |

| 3Fh | 3Fh | MLAT         | Maximum Latency                             |

Table 18: Identifier Register

| Bits  | Туре | Default Value | Description |

|-------|------|---------------|-------------|

| 31:16 | RO   | 1321h         | Device ID   |

| 0:15  | RO   | 1B4Bh         | Vendor ID   |

Table 19: Command Register

| Bits  | Туре | Default Value | Description                              |

|-------|------|---------------|------------------------------------------|

| 15:11 | RO   | 0h            | Reserved                                 |

| 10    | RW   | 0h            | Interrupt Disable                        |

| 9     | RO   | 0h            | Fast Back-to-Back Enable (N/A)           |

| 8     | RW   | 0h            | SERR# Enable (N/A)                       |

| 7     | RO   | 0h            | IDSEL Stepping/Wait Cycle Control (N/A)  |

| 6     | RW   | 0h            | Parity Error Response Enable             |

| 5     | RO   | 0h            | VGA Palette Snooping Enable (N/A)        |

| 4     | RO   | 0h            | Memory Write and Invalidate Enable (N/A) |

| 3     | RO   | 0h            | Special Cycle Enable (N/A)               |

| 2     | RW   | 0h            | Bus Master Enable                        |

| 1     | RW   | 0h            | Memory Space Enable                      |

| 0 | RW | 0h | I/O Space Enable |

|---|----|----|------------------|

|---|----|----|------------------|

Table 20: Status Register

| Fable 20: Status Register Bits | Туре  | Default Value | Description                                 |

|--------------------------------|-------|---------------|---------------------------------------------|

|                                | 1,700 | 2014411114141 | 2000/15/1011                                |

| 15                             | RW    | 0h            | Detected Parity Error                       |

| 14                             | RW    | 0h            | Signaled System Error                       |

| 13                             | RW    | 0h            | Received Master Abort                       |

| 12                             | RW    | 0h            | Received Target Abort                       |

| 11                             | RW    | 0h            | Signaled Target Abort (N/A)                 |

| 10:9                           | RO    | 0h            | DEVSEL Timing (N/A)                         |

| 8                              | RW    | 0h            | Master Data Parity Error Detected           |

| 7                              | RO    | 0h            | Fast Back-to-Back Transaction Capable (N/A) |

| 6                              | RO    | 0h            | Reserved                                    |

| 5                              | RO    | 0h            | 66MHz Capable (N/A)                         |

| 4                              | RO    | 1h            | Capabilities List                           |

| 3                              | RO    | 0h            | Interrupt Status                            |

| 2:1                            | RO    | 0h            | Reserved                                    |

| 0                              | RO    | 0h            | Reserved                                    |

Table 21: Revision ID Register

| Bits | Туре | Default Value | Description                     |

|------|------|---------------|---------------------------------|

| 7:0  | RO   | 02h           | Controller Hardware Revision ID |

Table 22: Class Code Register

| Bits  | Туре | Default Value | Description           |

|-------|------|---------------|-----------------------|

| 23:16 | RO   | 01h           | Base Class Code       |

| 15:8  | RO   | 08h           | Sub Class Code        |

| 7:0   | RO   | 02h           | Programming Interface |

Table 23: Cache Line Size Register

| Bits | Туре | Default Value | Description           |

|------|------|---------------|-----------------------|

| 7:0  | RW   | 0h            | Cache Line Size (N/A) |

Table 24: Master Latency Timer Register

| Bits | Туре | Default Value | Description                |

|------|------|---------------|----------------------------|

| 7:0  | RO   | 0h            | Master Latency Timer (N/A) |

Table 25: Header Type Register

| Bits | Туре | Default Value | Description                 |

|------|------|---------------|-----------------------------|

| 7    | RO   | 0h            | Multi-Function Device (N/A) |

| 6:0  | RO   | 0h            | Reserved                    |

Table 26: Built In Self Test Register

| Bits | Туре | Default Value | Description              |

|------|------|---------------|--------------------------|

| 7:0  | RO   | 0h            | Built In Self Test (N/A) |

Table 27: Memory Register Base Address Lower 32-bits (BAR0) Register

| Bits  | Туре | Default Value | Description                    |

|-------|------|---------------|--------------------------------|

| 31:14 | RW   | 0h            | Base Address                   |

| 13:4  | RO   | 0h            | Reserved                       |

| 3     | RO   | 0h            | Pre-Fetchable                  |

| 2:1   | RO   | 2h            | Address Type (64-bit)          |

| 0     | RO   | 0h            | Memory Space Indicator (MEMSI) |

Table 28: Memory Register Base Address Upper 32-bits (BAR1)

| Bits | Туре | Default Value | Description  |

|------|------|---------------|--------------|

| 31:0 | RO   | 0h            | Base Address |

Table 29: Index/Data Pair Register Base Address (BAR2) Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

| 31:0 | RO   | 0h            | N/A         |

Table 30: BAR3 Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

| 31:0 | RO   | 0h            | N/A         |

Table 31: Vendor Specific BAR4 Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

|      |      |               |             |

|  |  | 31:0 | RO | 0h | N/A |

|--|--|------|----|----|-----|

|--|--|------|----|----|-----|

Table 32: Vendor Specific BAR5 Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

| 31:0 | RO   | 0h            | N/A         |

Table 33: Card bus CIS Pointer Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

| 31:0 | RO   | 0h            | N/A         |

Table 34: Subsystem Identifier Register

| Bits  | Туре | Default Value | Description         |

|-------|------|---------------|---------------------|

| 31:16 | RO   | 0100h         | Subsystem ID        |

| 15:0  | RO   | 1B4Bh         | Subsystem Vendor ID |

Table 35: Expansion ROM Register

| Bits  | Туре | Default Value | Description                  |

|-------|------|---------------|------------------------------|

| 31:17 | RW   | 0h            | Expansion ROM Base Address   |

| 16:1  | RO   | 0h            | Reserved                     |

| 0     | RW   | 0h            | Expansion ROM Enable/Disable |

Table 36: Capabilities Pointer Register

| Bits | Туре | Default Value | Description                                                            |

|------|------|---------------|------------------------------------------------------------------------|

| 7:0  | RO   | 40h           | Capability Pointer  (Points to PCI Power Management Capability Offset) |

|      |      |               | (* 1 12 · 1 1                                                          |

Table 37: Interrupt Information Register

| Bits | Туре | Default Value | Description    |

|------|------|---------------|----------------|

| 15:8 | RO   | 01h           | Interrupt Pin  |

| 7:0  | RW   | 0h            | Interrupt Line |

Table 38: Minimum Grant Register

| Bits | Туре | Default Value | Description   |

|------|------|---------------|---------------|

| 7:0  | RO   | 0h            | Minimum Grant |

Table 39: Maximum Latency Register

| Bits | Туре | Default Value | Description     |

|------|------|---------------|-----------------|

| 7:0  | RO   | 0h            | Maximum Latency |

#### 8.1.3 PCI Power Management Register

Table 40: PCI Power Management Capability Register Summary

| Start Address | End Address | Symbol        | Description                             |

|---------------|-------------|---------------|-----------------------------------------|

| 40h           | 40h         | PCIPM_ID      | PCI Power Management Capability ID      |

| 41h           | 41h         | NEXTCAP       | Next Capability Pointer                 |

| 42h           | 43h         | PCIPM_ID      | PC Power Management Capabilities        |

| 44h           | 45h         | PCIPM_CS      | PCI Power Management Control and Status |

| 46h           | 46h         | PCIPM_CSR_BSE | PMCSR_BSE Bridge Extensions             |

| 47h           | 47h         | PCIPM_DATA    | Data                                    |

Table 41: PCI Power Management Capability ID Register

| Bits | Туре | Default Value | Description     |

|------|------|---------------|-----------------|

| 15:8 | RO   | 50h           | Next Capability |

| 7:0  | RO   | 01h           | Capability ID   |

Table 42: PCI Power Management Capability Register

| Bits  | Туре | Default Value | Description                                                        |

|-------|------|---------------|--------------------------------------------------------------------|

| 15:11 | RO   | 19h           | PME Support (N/A)                                                  |

| 10    | RO   | 0h            | D2 Support (N/A)                                                   |

| 9     | RO   | 0h            | D1 Support (N/A)                                                   |

| 8:6   | RO   | 0h            | AUX Current (N/A)                                                  |

| 5     | RO   | 0h            | Device Specific Initialization (N/A)                               |

| 4     | RO   | 0h            | Reserved                                                           |

| 3     | RO   | 0h            | PME Clock (N/A)                                                    |

| 2:0   | RO   | 3h            | Version (Support for PCI Bus Power Management Interface Spec R1.2) |

Table 43: PCI Power Management Control and Status Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

|      |      |               |             |

| 31:24 | RO | 0h | Data register (N/A)          |

|-------|----|----|------------------------------|

| 23    | RO | 0h | Bus Power/Clock Enable (N/A) |

| 22    | RO | 0h | B2, B3support (N/A)          |

| 21:16 | RO | 0h | Reserved                     |

| 15    | RO | 0h | PME Status(N/A)              |

| 14:13 | RO | 0h | Data Scale (N/A)             |

| 12:9  | RO | 0h | Data Select (N/A)            |

| 8     | RW | 0h | PME enable (N/A)             |

| 7:4   | RO | 0h | Reserved                     |

| 3     | RO | 1h | No Soft Reset                |

| 2     | RO | 0h | Reserved                     |

| 1:0   | RW | 0h | Power State                  |

### 8.1.4 Message Signaled Interrupt Register

Table 44: Message Signaled Interrupt Capability Register Summary

| Start Address | End Address | Symbol    | Description                                |

|---------------|-------------|-----------|--------------------------------------------|

| 50h           | 51h         | MSI_ID    | Message Signaled Interrupt Capability ID   |

| 52h           | 53h         | MSI_MC    | Message Signaled Interrupt Message Control |

| 54h           | 57h         | MSI_MA    | Message Signaled Interrupt Message Address |

| 58h           | 5Bh         | MSI_MUA   | Message Signaled Interrupt Upper Address   |

| 5Ch           | 5Dh         | MSI_MDATA | Message Signaled Interrupt Message Data    |

| 60h           | 63h         | MSI_MMASK | Message Signaled Interrupt Mask Bits       |

| 64h           | 67h         | MSI_MPEND | Message Signaled Interrupt Pending Bits    |

Table 45: Message Signaled Interrupt Capability ID Register

| Bits | Туре | Default Value | Description     |

|------|------|---------------|-----------------|

| 15:8 | RO   | 70h           | Next Capability |

| 7:0  | RO   | 05h           | Capability ID   |

Table 46: Message Signaled Interrupt Control Register

| Bits | Туре | Default Value | Description                |

|------|------|---------------|----------------------------|

| 15:9 | RO   | 0h            | Reserved                   |

| 8    | RO   | 1h            | Per Vector Masking Capable |

| 7    | RO   | 1h            | 64-bit Address Capable     |

| 6:4  | RW   | 0h            | Multiple Message Enable    |

| 3:1  | RO   | 0h            | Multiple Message Capable   |

| 0    | RW   | 0h            | MSI Enable                 |

Table 47: Message Signaled Interrupt Lower Address Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

| 31:2 | RW   | 0h            | Address     |

| 1:0  | RO   | 0h            | Reserved    |

Table 48: Message Signaled Interrupt Upper Address Register

| Bits | Туре | Default Value | Description   |

|------|------|---------------|---------------|

| 31:0 | RW   | 0h            | Upper Address |

Table 49: Message Signaled Interrupt Message Data Register

| Bits  | Туре | Default Value | Description |

|-------|------|---------------|-------------|

| 31:16 | RO   | 0h            | Reserved    |

| 0:15  | RW   | 0h            | Data        |

Table 50: Message Signaled Interrupt Mask Bits Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

| 31:0 | RW   | 0h            | Mask Bits   |

Table 51: Message Signaled Interrupt Pending Bits Register

| Bits | Туре | Default Value | Description  |

|------|------|---------------|--------------|

| 31:0 | RO   | 0h            | Pending Bits |

#### 8.1.5 PCI Express Capability Register

Table 52: PCI Express Capability Register Summary

| Start Address | End Address | Symbol | Description |

|---------------|-------------|--------|-------------|

|               |             |        |             |

| 70h | 71h | PCIE_ID    | PCI Express Capability ID         |

|-----|-----|------------|-----------------------------------|

| 72h | 73h | PCIE_CAP   | PCI Express Capabilities          |

| 74h | 77h | PCIE_DCAP  | PCI Express Device Capabilities   |

| 78h | 79h | PCIE_DC    | PCI Express Device Control        |

| 7Ah | 7Bh | PCIE_DS    | PCI Express Device Status         |

| 7Ch | 7Fh | PCIE_LCAP  | PCI Express Link Capabilities     |

| 80h | 81h | PCIE_LC    | PCI Express Link Control          |

| 82h | 83h | PCIE_LS    | PCI Express Link Status           |

| 94h | 97h | PCIE_DCAP2 | PCI Express Device Capabilities 2 |

| 98h | 99h | PCIE_DC2   | PCI Express Device Control 2      |

| 9Ah | 9Bh | PCIE_DS2   | PCI Express Device Status 2       |

| 9Ch | 9Fh | PCIE_LCAP2 | PCI Express Link Capabilities 2   |

| A0h | A1h | PCIE_LC2   | PCI Express Link Control 2        |

| A2h | A3h | PCIE_LS2   | PCI Express Link Status 2         |

Table 53: PCI Express Capability ID Register

| Bits | Туре | Default Value | Description                     |

|------|------|---------------|---------------------------------|

| 15:8 | RO   | B0h           | Next Pointer (MSI-X Capability) |

| 7:0  | RO   | 10h           | Capability ID                   |

Table 54: PCI Express Capabilities Register

| Bits  | Туре | Default Value | Description               |

|-------|------|---------------|---------------------------|

| 15:14 | RO   | 0h            | Reserved                  |

| 13:9  | RO   | 0h            | Interrupt Message Number  |

| 8     | RW   | 0h            | Slot Implementation (N/A) |

| 7:4   | RO   | 0h            | Device/Port Type          |

| 3:0   | RO   | 2h            | Capability Version        |

Table 55: PCI Express Device Capabilities Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

| -     | 1  |    |                                               |

|-------|----|----|-----------------------------------------------|

| 31:29 | RO | 0h | Reserved                                      |

| 28    | RO | 1h | Function Level Reset Capability               |

| 27:26 | RO | 0h | Captured Slot Power Limit Scale               |

| 25:18 | RO | 0h | Captured Slot Power Limit Value               |

| 17:16 | RO | 0h | Reserved                                      |

| 15    | RO | 1h | Role-based Error Reporting                    |

| 14:12 | RO | 0h | Reserved                                      |

| 11:9  | RO | 7h | Endpoint L1 Acceptable Latency                |

| 8:6   | RO | 7h | Endpoint L0 Acceptable Latency                |

| 5     | RO | 0h | Extended Tag Field Supported                  |

| 4:3   | RO | 0h | Phantom Functions Supported                   |

| 2:0   | RO | 2h | Max Payload Size Supported (512 payload size) |

Table 56: PCI Express Device Control Register

| able 56: PCI Express Device Control Register |                                  |                                                                                                                             |  |  |  |

|----------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Туре                                         | Default Value                    | Description                                                                                                                 |  |  |  |

| RW                                           | 0h                               | Initiate Function Level Reset                                                                                               |  |  |  |

| RW                                           | 2h                               | Max Read Request Size                                                                                                       |  |  |  |

| RW                                           | 0h                               | Enable No Snoop                                                                                                             |  |  |  |

| RW                                           | 0h                               | Aux Power PM Enable (N/A)                                                                                                   |  |  |  |

| RW                                           | 0h                               | Phantom Functions Enable (N/A)                                                                                              |  |  |  |

| RW                                           | 0h                               | Extended Tag Enable                                                                                                         |  |  |  |

| RW                                           | 0h                               | Max Payload Size                                                                                                            |  |  |  |

| RW                                           | 1h                               | Enable Relaxed Ordering                                                                                                     |  |  |  |

| RW                                           | 0h                               | Unsupported Request Reporting Enable                                                                                        |  |  |  |

| RW                                           | 0h                               | Fatal Error Reporting Enable                                                                                                |  |  |  |

| RW                                           | 0h                               | Non-Fatal Error Reporting Enable                                                                                            |  |  |  |

| RW                                           | 0h                               | Correctable Error Reporting Enable                                                                                          |  |  |  |

|                                              | RW | Type Default Value  RW 0h  RW 2h  RW 0h  RW 0h |  |  |  |

Table 57: PCI Express Device Status Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

| 15:6 | RO   | 0h            | Reserved    |

| 5 | RO | 0h | Transactions Pending         |

|---|----|----|------------------------------|

| 4 | RO | 0h | Aux Power Detected           |

| 3 | RW | 0h | Unsupported Request Detected |

| 2 | RW | 0h | Fatal Error Detected         |

| 1 | RW | 0h | Non-Fatal Error Detected     |

| 0 | RW | 0h | Correctable Error Detected   |

| Table 58: PCI Express Link Capabilities Register |      |               |                                                     |  |  |

|--------------------------------------------------|------|---------------|-----------------------------------------------------|--|--|

| Bits                                             | Туре | Default Value | Description                                         |  |  |

| 31:24                                            | RW   | 0h (Port 0)   | Port Number                                         |  |  |

| 23                                               | RO   | 0h            | Reserved                                            |  |  |

| 22                                               | RW   | 1h            | ASPM Optionality Compliance                         |  |  |

| 21                                               | RO   | 0h            | Link Bandwidth Notification Capability (N/A)        |  |  |

| 20                                               | RO   | 0h            | Data Link Layer Link Active Reporting Capable (N/A) |  |  |

| 19                                               | RO   | 0h            | Surprise Down Error Reporting Capable (N/A)         |  |  |

| 18                                               | RO   | 1h            | Clock Power Management                              |  |  |

| 17:15                                            | RO   | 6h            | L1 Exit Latency                                     |  |  |

| 14:12                                            | RO   | 7h            | L0s Exit Latency                                    |  |  |

| 11:10                                            | RO   | 2h            | Active State Power Management Support               |  |  |

| 9:4                                              | RO   | 4h            | Maximum Link Width                                  |  |  |

| 3:0                                              | RO   | 4h            | Supported Link Speeds                               |  |  |

Table 59: PCI Express Link Control Register

| Bits  | Туре | Default Value | Description                                      |

|-------|------|---------------|--------------------------------------------------|

| 15:14 | RO   | 0h            | DRS Signaling Control                            |

| 13:12 | RW   | 0h            | Reserved                                         |

| 11    | RW   | 0h            | Link Autonomous Bandwidth Interrupt Enable (N/A) |

| 10    | RW   | 0h            | Link Bandwidth Management Interrupt Enable (N/A) |

| 9     | RW   | 0h            | Hardware Autonomous Width Disable                |

| 8     | RW   | 0h            | Enable Clock Power Management                    |

| 7     | RW   | 0h            | Extended Sync                                    |

| 6   | RW | 0h | Common Clock Configuration            |

|-----|----|----|---------------------------------------|

| 5   | RW | 0h | Retrain Link                          |

| 4   | RW | 0h | Link Disable                          |

| 3   | RW | 0h | Read Completion Boundary              |

| 2   | RO | 0h | Reserved                              |

| 1:0 | RW | 0h | Active State Power Management Control |

Table 60: PCI Express Link Status Register

| Bits | Туре | Default Value | Description                      |

|------|------|---------------|----------------------------------|

| 15   | RO   | 0h            | Link Autonomous Bandwidth Status |

| 14   | RO   | 0h            | Link Bandwidth Management Status |

| 13   | RO   | 0h            | Data Link Layer Link Active      |

| 12   | RW   | 1h            | Slot Clock Configuration         |

| 11   | RO   | 0h            | Link Training                    |

| 10   | RO   | 0h            | Reserved                         |

| 9:4  | RO   | 1h            | Negotiated Link Width            |

| 3:0  | RO   | 1h            | Current Link Speed               |

Table 61: PCI Express Device Capabilities 2 Register

| Bits  | Туре | Default Value | Description                                |

|-------|------|---------------|--------------------------------------------|

| 31    | RW   | 1h            | FRS Supported                              |

| 30:20 | RO   | 0h            | Reserved                                   |

| 19:18 | RO   | 0h            | OBFF Supported                             |

| 17:16 | RO   | 0h            | Reserved                                   |

| 15:14 | RO   | 0h            | LN System CLS (N/A)                        |

| 13:12 | RO   | 0h            | TPH Completer Supported (N/A)              |

| 11    | RO   | 1h            | Latency Tolerance Reporting Supported      |

| 10    | RO   | 0h            | No RO-enabled PR-PR Passing (N/A)          |

| 9     | RO   | 0h            | 128-bit CAS Completer Supported (N/A)      |

| 8     | RO   | 0h            | 64-bit Atomic Op Completer Supported (N/A) |

| 7     | RO   | 0h            | 32-bit Atomic Op Completer Supported (N/A) |

| 6     | RO   | 0h            | Atomic Op Routing Supported (N/A)          |

| 5   | RO | 0h | ARI Forwarding Supported (N/A)       |

|-----|----|----|--------------------------------------|

| 4   | RO | 1h | Completion Timeout Disable Supported |

| 3:0 | RO | Fh | Completion Timeout Ranges Supported  |

Table 62: PCI Express Device Control 2 Register

| Table 62. FCI Express Device Control 2 Register |      |               |                                              |  |

|-------------------------------------------------|------|---------------|----------------------------------------------|--|

| Bits                                            | Туре | Default Value | Description                                  |  |

| 15:11                                           | RO   | 0h            | Reserved                                     |  |

| 10                                              | RW   | 0h            | Latency Tolerance Reporting Mechanism Enable |  |

| 9:6                                             | RO   | 0h            | Reserved                                     |  |

| 5                                               | RW   | 0h            | ARI Forwarding Enable                        |  |

| 4                                               | RW   | 0h            | Completion Timeout Disable                   |  |

| 3:0                                             | RW   | 0h            | Completion Timeout Value                     |  |

Table 63: PCI Express Device Status 2 Register

| Bits | Туре | Default Value | Description |

|------|------|---------------|-------------|

| 15:0 | RO   | 0h            | Reserved    |

Table 64: PCI Express Link Capabilities 2 Register

| Bits  | Туре | Default Value | Description                         |

|-------|------|---------------|-------------------------------------|

| 31    | RO   | 1h            | DRS Supported                       |

| 30:25 | RO   | 0h            | Reserved                            |

| 24    | RW   | 1h            | Two Retimer Presence Detect Support |

| 23    | RW   | 1h            | Retimer Presence Detect Support     |

| 22:9  | RO   | 0h            | Reserved                            |

| 8     | RO   | 0h            | Cross-Link Supported (N/A)          |

| 7:1   | RO   | Fh            | Supported Speeds Vector             |

| 0     | RO   | 0h            | Reserved                            |

Table 65: PCI Express Link Control 2 Register

| Bits  | Туре | Default Value | Description               |

|-------|------|---------------|---------------------------|

| 15:12 | RW   | Oh            | Compliance De-emphasis    |

| 11    | RW   | 0             | Compliance SOS            |

| 10    | RW   | 0             | Enter Modified Compliance |

| 9:7 | RW     | 0h | Transmit Margin                   |

|-----|--------|----|-----------------------------------|

| 6   | RW     | 0  | Selectable De-Emphasis (N/A)      |

| 5   | RW     | 0  | Hardware Autonomous Speed Disable |

| 4   | RW     | 0  | Enter Compliance                  |

|     |        |    | Target Link Speed                 |

|     |        |    | 1h: 2.5 GT/s (Gen 1)              |

| 3:0 | 3:0 RW | 4h | 2h: 5.0 GT/s (Gen 2)              |

|     |        |    | 3h: 8 GT/s (Gen 3)                |

|     |        |    | 4h: 16 GT/s(Gen 4)                |

Table 66: PCI Express Link Status 2 Register

| Table 66: PCI Express Link |      |               |                                 |

|----------------------------|------|---------------|---------------------------------|

| Bits                       | Туре | Default Value | Description                     |

| 15:6                       | RO   | 0             | Reserved                        |

| 5                          | RW   | 0             | Link Equalization Request       |

| 4                          | RO   | 0             | Equalization Phase 3 Successful |

| 3                          | RO   | 0             | Equalization Phase 2 Successful |

| 2                          | RO   | 0             | Equalization Phase 1 Successful |

| 1                          | RO   | 0             | Equalization Complete           |

| 0                          | RO   | 1             | Current De-Emphasis             |

#### 8.1.6 MSI-X Register

Table 67: MSI-X Capability Register Summary

| Start Address | End Address | Symbol   | Description                      |

|---------------|-------------|----------|----------------------------------|

| B0h           | B1h         | MSIX_ID  | MSI-X Capability ID              |

| B2h           | B3h         | MSIX_CAP | MSI-X Message Control            |

| B4h           | B7h         | MSIX_TBL | MSI-X Table Offset and Table BIR |

| B8h           | BBh         | MSIX_PBA | MSI-X PBA Offset and PBA BIR     |

Table 68: MSI-X Identifier Register

| ſ   | Bits | Туре | Default Value | Description |

|-----|------|------|---------------|-------------|

| - 1 |      |      |               |             |

| 15:8 | RO | 00h | Next Capability |

|------|----|-----|-----------------|

| 7:0  | RO | 11h | Capability ID   |

Table 69: MSI-X Control Register

| Bits  | Туре | Default Value | Description   |

|-------|------|---------------|---------------|

| 15    | RW   | 0             | MSI-X Enable  |

| 14    | RW   | 0             | Function Mask |

| 13:11 | RO   | 0h            | Reserved      |

| 10:0  | RO   | 42h           | Table Size    |

Table 70: MSI-X Table Offset Register

| Bits | Туре | Default Value | Description  |

|------|------|---------------|--------------|

| 31:3 | RO   | 400h          | Table Offset |

| 2:0  | RO   | 0             | Table BIR    |

Table 71: MSI-X Pending Bit Array Offset Register

| Bits | Туре | Default Value | Description              |

|------|------|---------------|--------------------------|

| 31:3 | RO   | 600h          | Pending Bit Array Offset |

| 2:0  | RO   | 0             | Pending Bit Array BIR    |

#### 8.1.7 Advanced Error Reporting Register

Table 72: Advanced Error Reporting Capability Register Summary

| Start Address | End Address | Symbol     | Description                                 |

|---------------|-------------|------------|---------------------------------------------|

| 100h          | 103h        | AER_ID     | AER Capability ID                           |

| 104h          | 107h        | AER_UCES   | AER Uncorrectable Error Status              |

| 108h          | 10Bh        | AER_UCEM   | AER Uncorrectable Error Mask                |

| 10Ch          | 10Fh        | AER_UCESEV | AER Uncorrectable Error Severity            |

| 110h          | 113h        | AER_CES    | AER Correctable Error Status                |

| 114h          | 117h        | AER_CEM    | AER Correctable Error Mask                  |

| 118h          | 11Bh        | AER_CC     | AER Advanced Error Capabilities and Control |

| 11Ch          | 12Bh        | AER_HL     | AER Header Log                              |

Table 73: AER Capability ID Register

| Bits  | Туре | Default Value | Description                                                                       |

|-------|------|---------------|-----------------------------------------------------------------------------------|

| 31:20 | RO   | 148h          | Next Pointer  (Points to Secondary PCI Express Extended Capability Header Offset) |

| 19:16 | RO   | 2h            | Capability Version                                                                |

| 15:0  | RO   | 1h            | Capability ID                                                                     |

| Table 74: AER Uncorrecta | able 74: AER Uncorrectable Error Status Register |               |                                           |  |  |  |

|--------------------------|--------------------------------------------------|---------------|-------------------------------------------|--|--|--|

| Bits                     | Туре                                             | Default Value | Description                               |  |  |  |

| 31:23                    | RO                                               | 0h            | Reserved                                  |  |  |  |

| 22                       | RW                                               | 0h            | Uncorrectable Internal Error Status (N/A) |  |  |  |

| 21                       | RO                                               | 0h            | Reserved                                  |  |  |  |

| 20                       | RW                                               | 0h            | Unsupported Request Error Status          |  |  |  |

| 19                       | RW                                               | 0h            | ECRC Error Status                         |  |  |  |

| 18                       | RW                                               | 0h            | Malformed TLP Status                      |  |  |  |

| 17                       | RW                                               | 0h            | Receiver Overflow Status                  |  |  |  |

| 16                       | RW                                               | 0h            | Unexpected Completion Status              |  |  |  |

| 15                       | RW                                               | 0h            | Completer Abort Status                    |  |  |  |

| 14                       | RW                                               | 0h            | Completion Timeout Status                 |  |  |  |

| 13                       | RW                                               | 0h            | Flow Control Protocol Error Status        |  |  |  |

| 12                       | RW                                               | 0h            | Poisoned TLP Status                       |  |  |  |