# **Multi-channel Half Bridge Driver**

Datasheet (EN) 1.0

### **Product Overview**

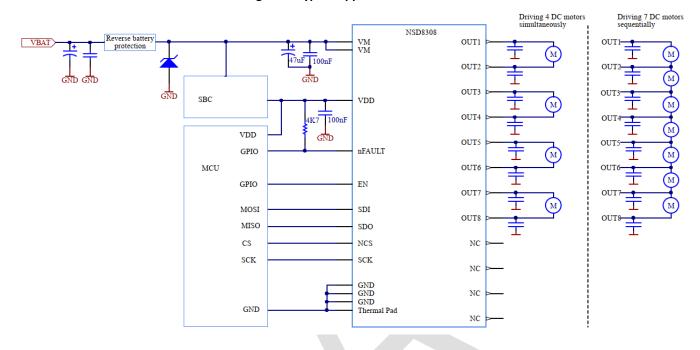

The NSD8308 is a multi-channel half-bridge driver for automotive applications including HVAC flap DC motors, side mirror adjustment / fold motors, general relays, or other LFDs.

With the different connection configuration of half-bridge power stage outputs, the device can driver DC motors in simultaneous, sequential, or parallel mode. The outputs also support DC motor in forward, reverse, slow decay, and fast decay operation.

The device includes 8x internal configurable PWM generators, which allow for flexible control for LED dimming or motor current limitation during start up or stall condition.

The integrated serial peripheral interface (SPI) controls all outputs and provides diagnostic information including normal operation, POR, VM undervoltage/overvoltage, overcurrent, over temperature protection and open load status.

The device features sleep mode with low quiescent current when EN input is low or VDD falls below POR threshold.

## **Applications**

- HVAC DC motors

- Side mirror adjustment and mirror fold

- Relays

- LEDs

### **Device Information**

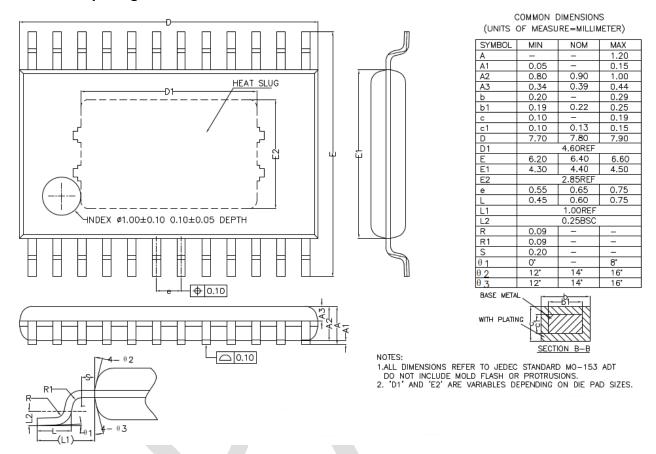

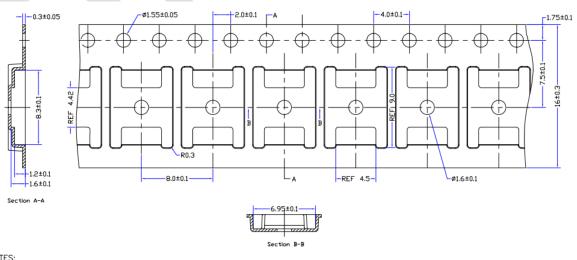

| Part Number     | Package  | Body Size       |

|-----------------|----------|-----------------|

| NSD8308-Q1HTSXR | HTSSOP24 | 7.80mm × 4.40mm |

## **Key Features**

- 8x half bridge driver

- HS/LS Rdson: 0.75ohm typ at 25°C

- Device 1A per HB channel, 3A max for all channel all on

- Half bridge output can be in parallel

- Wide 4.5V to 36V (configurable) operating Voltage

- Very low quiescent sleep mode

- PWM mode with internal PWM generation on each channel

- 4 PWM frequency options: 80Hz/100Hz/200Hz/2000 Hz

- 8-bit duty resolution (1/255, ~0.4 % duty)

- Slew rate control for supporting 200, 2000Hz

- Integrated diagnosis and fault protection features

- VM undervoltage & overvoltage protection (UV&OV)

- Overcurrent / short circuit Protection (OCP/SCP)

- Over temperature warning & shutdown

- Open load diagnosis

- Dedicated nFault indicator pin

- HTSSOP24, 7.8mm X 4.4mm with exposed PAD

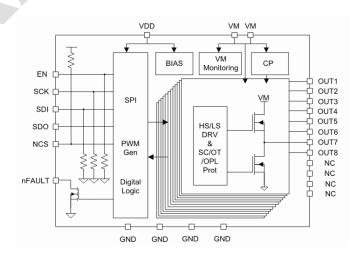

## **Functional Block Diagrams**

Figure 1. NSD8308 Block Diagram

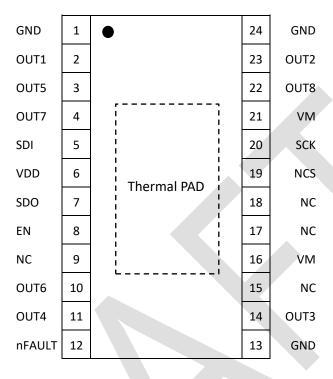

# 1. Pin Configuration and Functions

Figure 2. NSD8308 Pinout

Table 1. NSD8308 Pin Description

| SYMBOL | NO.            | TYPE | DESCRIPTION                                                                                                                                                      |

|--------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND    | 1,13,<br>24    | PWR  | Pins for ground connection, all ground pins should be externally connected together.                                                                             |

| OUT1   | 2              | 0    | Half-bridge output1 pin.                                                                                                                                         |

| OUT5   | 3              | 0    | Half-bridge output5 pin.                                                                                                                                         |

| OUT7   | 4              | 0    | Half-bridge output7 pin.                                                                                                                                         |

| SDI    | 5              | I    | SPI data input pin                                                                                                                                               |

| VDD    | 6              | PWR  | Logic supply input pin,                                                                                                                                          |

| SDO    | 7              | 0    | SPI data output pin                                                                                                                                              |

| EN     | 8              | ı    | Driver enable input pin with internal pull down (active HIGH). If EN input pin is pulled low, all OUTx go to tri-state and device move to low-power sleep state. |

| NC     | 9,15,<br>17,18 | -    | Not connected                                                                                                                                                    |

| OUT6           | 10    | 0   | Half-bridge output6 pin.                                                                                                                                                                                                                                                                   |

|----------------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT4           | 11    | 0   | Half-bridge output4 pin.                                                                                                                                                                                                                                                                   |

| nFAULT         | 12    | 0   | Fault alert indicator output (active LOW). Open drain structure requires external pull up resistor, typical 4.7Kohm can be used.                                                                                                                                                           |

| OUT3           | 14    | 0   | Half-bridge output3 pin.                                                                                                                                                                                                                                                                   |

| VM             | 16,21 | PWR | 5V to 36V power supply. Connect a 0.1-μF bypass capacitor to ground, as well as sufficient bulk capacitor (>10uF) needs to guarantee VM pin voltage in maximum range.  Put the 0.1uF and bulk capacitor (>10uF) close to the VM pin.  Two VM pins should be externally connected together. |

| NCS            | 19    | ı   | SPI chip select input pin.                                                                                                                                                                                                                                                                 |

| SCK            | 20    | I   | SPI clock input pin.                                                                                                                                                                                                                                                                       |

| OUT8           | 22    | 0   | Half-bridge output8 pin.                                                                                                                                                                                                                                                                   |

| OUT2           | 23    | 0   | Half-bridge output2 pin.                                                                                                                                                                                                                                                                   |

| Thermal<br>PAD | _     |     | Thermal pad. Connect to board ground. For good thermal dissipation, use large ground planes on multiple layers, and multiple nearby vias connecting those planes.                                                                                                                          |

# 2. Absolute Maximum Ratings

| SYMBOL                                                                                                                  | PARAMETER                                                  | MIN  | MAX     | UNIT |

|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|---------|------|

| VM                                                                                                                      | Power supply voltage                                       | -0.3 | 40      | V    |

| VDD                                                                                                                     | Logic supply voltage                                       | -0.3 | 6       | V    |

| V <sub>SDI</sub> , V <sub>SDO</sub> ,<br>V <sub>NCS</sub> , V <sub>SCK</sub> ,<br>V <sub>EN</sub> , V <sub>nFAULT</sub> | Logic input/ouput voltage (EN, SDI, SDO, NCS, SCK, nFAULT) | -0.3 | VDD+0.3 | V    |

| V                                                                                                                       | Output voltage (OUTx) DC condition                         | -0.3 | 40      | V    |

| V <sub>OUTX</sub>                                                                                                       | Output voltage (OUTx) AC condition, lout=1A for t<500ms    | -1   | 40      | V    |

## 3. ESD Ratings

| SYMBOL   | PARAMETER                                                               | VALUE | UNIT |

|----------|-------------------------------------------------------------------------|-------|------|

| VESD_HBM | Human Body Model (HBM), VMx & VOUTx pins per ANSI/ESDA/JEDEC JS-001     | ±4000 | ٧    |

|          | Human Body Model (HBM), other pins per ANSI/ESDA/JEDEC JS-001           | ±2000 | V    |

| VESD_CDM | Charged device model (CDM), Corner pins, per JEDEC specification JS-002 | ±750  | V    |

|          | Charged device model (CDM), other pins, per JEDEC specification JS-002  | ±500  | V    |

## 4. Recommended Operating Conditions

| SYMBOL                               | PARAMETER                             | MIN | TYP | MAX | UNIT |

|--------------------------------------|---------------------------------------|-----|-----|-----|------|

|                                      | VM supply, normal voltage range       | 4.5 |     | 18  | V    |

| VM                                   | VM supply, extended voltage range (1) |     |     | Vov | V    |

|                                      | VM supply, over voltage range (2)     | Vov |     | 40  | V    |

| VDD                                  | VDD supply voltage                    | 3   |     | 5.5 | V    |

| EN, NCS,<br>SCK, SDO,<br>SDI, nFAULT | Logic input / output voltage          | 0   |     | 5.5 | V    |

<sup>(1)</sup> Device is capable of full functional operation; however, parameter characteristic is not guarantee, deviation is possible.

<sup>(2)</sup> No damage to device, and power stage will be disabled during overvoltage range. Full functional operation will resume when battery voltage returns to normal voltage range.

## 5. Thermal Information

| SYMBOL | DESCRIPTION                                                                     | MIN | TYP | MAX | UNIT |

|--------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| Та     | Ambient operating ambient temperature                                           | -40 |     | 125 | °C   |

| Tj     | Junction temperature                                                            | -40 |     | 150 | °C   |

| Tstg   | Storage temperature                                                             | -65 |     | 150 | °C   |

| Rthjc  | Thermal resistance, junction to case                                            |     | 2.7 |     | °C/W |

|        | Thermal resistance, junction to ambient, on 2-layer PCB                         |     | 62  |     | °C/W |

| Rthja  | Thermal resistance, junction to ambient, on 4-layer PCB based on JEDEC standard |     | 30  |     | °C/W |

## 6. Electrical characteristics

$T_j$  = -40°C to 150°C, VM=4.5V to 18V, VDD=3.0 to 5V, unless otherwise specified.

| SYMBOL                | PARAMETER                     | TEST CONDITIONS                                              | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------|--------------------------------------------------------------|-----|-----|-----|------|

| POWER SUI             | PPLY (VM)                     |                                                              |     |     |     |      |

|                       | VM operating supply           | VM = 13.5V, EN=HIGH, all output off                          |     | 0.5 | 1   | mA   |

| I <sub>VM</sub>       | current                       | VM = 13.5V, EN=HIGH, all high side on                        |     |     | 5   | mA   |

| I <sub>VM_SLEEP</sub> | VM sleep current              | VM = 13.5V, -40≤Tj≤85°C, EN=LOW, total current of all VM pin |     |     | 3   | μА   |

|                       | VM undervoltage               | VM falls until UVLO triggers                                 | 3.6 |     | 4.1 | V    |

| Vuv                   | threshold                     | VM rises until operation recovers                            | 3.9 |     | 4.4 | V    |

| V <sub>UV_HYS</sub>   | VM undervoltage hysteresis    |                                                              |     | 400 |     | mV   |

| tuv                   | VM undervoltage deglitch time | Guaranteed by digital scan                                   |     | 10  |     | us   |

|                       |                               | VM increasing, switch off, OVP_H = 0                         | 21  |     | 25  | V    |

|                       | VAA                           | VM decreasing, switch on, OVP_H = 0                          | 19  |     | 23  | V    |

| $V_{OV}$              | VM overvoltage                | VM increasing, switch off, OVP_H = 1                         | 32  |     | 36  | V    |

|                       |                               | VM decreasing, switch on, OVP_H = 1                          | 30  |     | 34  | V    |

| V <sub>OV_HYS</sub>   | VM overvoltage hysteresis     |                                                              |     | 2   |     | V    |

| tov                   | VM overvoltage deglitch time  | Guaranteed by digital scan                                   |     | 10  |     | us   |

| VDD SUPPL                | Y INPUT (VDD)                            |                                                                                            |             |      |             |    |

|--------------------------|------------------------------------------|--------------------------------------------------------------------------------------------|-------------|------|-------------|----|

|                          |                                          | EN=High, all outputs off, SPI not active                                                   |             |      | 3           | mA |

| IVDD                     | Input current of VDD                     | EN=High, SPI active 5MHz, all high side on                                                 |             |      | 5           | mA |

| I <sub>VDD_SLEEP</sub>   | Input current of VDD in sleep mode       | EN=LOW, SPI inactive<br>-40≤Tj≤85°C                                                        |             | 1    | 2.5         | uA |

| V <sub>VDD_POR_H</sub>   | POR high threshold                       | VDD increasing                                                                             | 2.5         |      | 3           | V  |

| V <sub>VDD_POR_L</sub>   | POR low threshold                        | VDD decreasing                                                                             | 2.3         |      | 2.8         | ٧  |

| LOGIC CON                | TROL INPUT (EN, NCS, SDI,                | SCK)                                                                                       |             |      |             |    |

| V <sub>IL</sub>          | Input logic low voltage                  |                                                                                            |             |      | 0.3*VD<br>D | ٧  |

| ViH                      | Input logic high voltage                 |                                                                                            | 0.7*<br>VDD |      |             | ٧  |

| V <sub>HYS</sub>         | Input logic hysteresis                   |                                                                                            |             | 0.5  |             | V  |

| R <sub>PD</sub>          | Pulldown resistance                      | EN, SDI, SCK                                                                               | 50          | 100  | 150         | kΩ |

| R <sub>PU</sub>          | Pullup resistance                        | NCS                                                                                        | 50          | 100  | 150         | kΩ |

| C <sub>IN</sub>          | Input capacitance                        | NCS, SDI, SCK pin, Specified by design                                                     |             |      | 15          | pF |

| $T_{Deglitch}$           | Deglitch filter on EN falling and rising |                                                                                            |             | 10   | 20          | us |

| T <sub>WAKE</sub>        | Wake-up time                             | After EN low to high                                                                       |             |      | 150         | us |

| NFAULT OU                | TPUT (OPEN DRAIN)                        |                                                                                            |             |      |             |    |

| $V_{OL\_nFault}$         | Output low voltage                       | I <sub>OD</sub> = 5mA                                                                      |             |      | 0.5         | V  |

| I <sub>LEAK_nFault</sub> | Output high leakage current              | V <sub>OD</sub> = 5V                                                                       | -1          |      | 1           | uA |

| SDO OUTPL                | JT (PUSH PULL)                           |                                                                                            |             |      |             |    |

| V <sub>OL_SDO</sub>      | SDO Output low voltage                   | Io = 2mA                                                                                   |             |      | 0.5         | ٧  |

| V <sub>OH_SDO</sub>      | SDO Output high voltage                  | Io = 2mA                                                                                   | VDD-<br>0.5 |      |             | ٧  |

| I <sub>LEAK_SDO</sub>    | SDO tristate leakage                     | NCS high, 0 <v<sub>SDO<vdd< td=""><td>-1</td><td></td><td>1</td><td>uA</td></vdd<></v<sub> | -1          |      | 1           | uA |

| C <sub>OUT</sub>         | Output capacitance                       | Specified by design                                                                        |             |      | 30          | pF |

| HALF BRIDG               | GE OUTPUS (OUT1, OUT2, O                 | DUT3, OUT4, OUT5, OUT6, OUT7, OUT8)                                                        |             |      |             |    |

|                          | High-side or Low-side                    | I = 0.5 A, Tj = 25°C                                                                       |             | 0.75 | 1.1         | Ω  |

| R <sub>DS(ON)</sub>      | FET on resistance                        | I = 0.5 A, Tj = 150°C                                                                      |             |      | 1.5         | Ω  |

| 1                     | HS OFF state leakage                   | VOUTx = 0V, EN = 1                                 | -2   | -1  | -    | uA   |

|-----------------------|----------------------------------------|----------------------------------------------------|------|-----|------|------|

| I <sub>LEAK_</sub> HS | HS OFF-state leakage                   | VOUTx = 0V, EN = 0                                 | -2   | -1  | -    | uA   |

|                       | IC OFF state lasks                     | VOUTx = 13.5V, EN = 1                              | -    | 1   | 2    | uA   |

| I <sub>LEAK_LS</sub>  | LS OFF-state leakage                   | VOUTx = 13.5V, EN = 0                              | -    | 1   | 2    | uA   |

| t <sub>RISE</sub>     | Output rise time                       | VM = 13.5 V, resistive load 100 ohm,<br>HBx_SR = 0 |      | 0.6 |      | V/µs |

| t <sub>FALL</sub>     | Output fall time High side or low side | VM = 13.5 V, resistive load 100 ohm,<br>HBx_SR = 1 |      | 2.5 |      | V/µs |

|                       | Propagation delay                      | HBx_SR = 0                                         | 5    | 12  | 25   | μs   |

| t <sub>PD</sub>       | (high side / low side ON/OFF)          | HBx_SR = 1                                         | 3    | 5   | 10   | μs   |

|                       | Cross protection time,                 | HBx_SR = 0                                         | 8    | 20  | 32   | μs   |

| t <sub>DEAD</sub>     | high to low / low to<br>high           | HBx_SR = 1                                         | 2    | 5   | 15   | μs   |

| OVERCURRE             | NT PROTECTION                          |                                                    |      |     |      |      |

| 1                     | Over current threshold                 | Half bridge low side                               | 1    |     | 1.6  | А    |

| l <sub>oc</sub>       |                                        | Half bridge high side                              | -1.6 |     | -1   | А    |

|                       |                                        | OC_Filter bit = 000                                |      | 10  |      |      |

|                       |                                        | OC_Filter bit = 001                                |      | 5   |      |      |

|                       |                                        | OC_Filter bit = 010                                |      | 2.5 |      |      |

|                       |                                        | OC_Filter bit = 011                                |      | 1   |      |      |

| toc                   | OC deglitch filter time                | OC_Filter bit = 100                                |      | 60  |      | μs   |

|                       |                                        | OC_Filter bit = 101                                |      | 40  |      |      |

|                       |                                        | OC_Filter bit = 110                                |      | 30  |      |      |

|                       |                                        | OC_Filter bit = 111                                |      | 20  |      |      |

| ON STATE O            | PEN LOAD DIAGNOSIS                     |                                                    |      |     |      |      |

|                       | Onen lead three hald                   | Half bridge low side, HBx_OPL_TH = 0               | 3    | 10  | 20   | mA   |

| l <sub>OL</sub>       | Open load threshold                    | Half bridge high side, HBx_OPL_TH = 0              | -20  | -10 | -3   | mA   |

| t <sub>OL</sub>       | Open load filter time                  | HBx_OPL_TH = 0, guarantee by digital scan          | 2    | 3   | 4    | ms   |

| I <sub>OL_LOW</sub>   | Low open load                          | Half bridge low side, HBx_OPL_TH = 1               | 0.3  | 1   | 2    | mA   |

|                       | threshold                              | Half bridge high side, HBx_OPL_TH = 1              | -2   | -1  | -0.3 | mA   |

|                       |                                        |                                                    |      |     |      |      |

# **NSD8308**

|                       |                                                                      | T                                         |                  |             | ı            |    |

|-----------------------|----------------------------------------------------------------------|-------------------------------------------|------------------|-------------|--------------|----|

| $t_{\text{OL\_LOW}}$  | Low open load filter time                                            | HBx_OPL_TH = 1, guarantee by digital scan | 0.2              | 0.3         | 0.4          | ms |

| ON STATE O            | OPEN LOAD DIAGNOSIS                                                  |                                           |                  |             |              |    |

|                       | Diag pull up current                                                 | HBx_IPUPD_MODE = 0                        | 133              | 200         | 266          | uA |

| I <sub>PU</sub>       | Diag pull up current                                                 | HBx_IPUPD_MODE = 1                        | 666              | 1           | 1.5          | mA |

|                       | Diag pull down current                                               | HBx_IPUPD_MODE = 0                        | 400              | 600         | 800          | uA |

| I <sub>PD</sub>       | Diag pull down current                                               | HBx_IPUPD_MODE = 1                        | 2                | 3           | 4.5          | mA |

| V <sub>STA_HB</sub>   | Off state status threshold                                           | OUTx pin                                  | 0.54<br>*VD<br>D | 0.6*V<br>DD | 0.66*V<br>DD | V  |

| THERMAL I             | PROTECTION                                                           |                                           |                  |             |              |    |

| OT <sub>WARN</sub>    | Thermal warning temperature                                          |                                           | 120              | 140         | 160          | °C |

| T <sub>HYS_OTW</sub>  | Thermal warning hysteresis                                           |                                           |                  | 20          |              | °C |

| OT <sub>SD</sub>      | Thermal shutdown temperature                                         |                                           | 150              | 170         | 190          | °C |

| T <sub>HYS_OTSD</sub> | Thermal shutdown hysteresis                                          |                                           |                  | 20          |              | °C |

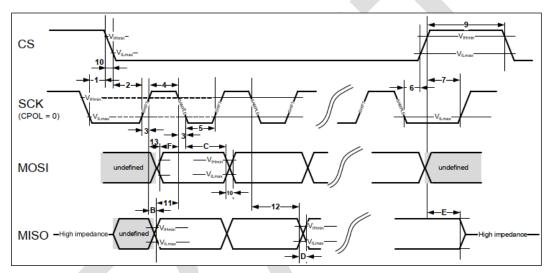

| SPI AC TIM            | INGS                                                                 |                                           |                  |             |              |    |

| T <sub>cll</sub>      | Minimum time CLK = LOW (5)                                           | Application info                          | 85               |             |              | ns |

| T <sub>clh</sub>      | Minimum time CLK = HIGH (4)                                          | Application info                          | 85               |             |              | ns |

| T <sub>pcld</sub>     | Propagation delay<br>(SCLK to data at SDO<br>active) (B)             | Cload=30pF                                |                  |             | 30           | ns |

| T <sub>lead</sub>     | CLK change L/H after<br>NCS = LOW (2)                                | Application info                          | 100              |             |              | ns |

| T <sub>scld</sub>     | SDI input setup time<br>(CLK change H/L after<br>SDI data valid) (F) | Application info                          | 30               |             |              | ns |

| T <sub>hcld</sub>     | SDI input hold time<br>(SDI data hold after<br>CLK change H/L) (C)   | Application info                          | 30               |             |              | ns |

| T <sub>sclch</sub>    | CLK low before NCS low (1)                                           | Application info                          | 125              |             |              | ns |

| T <sub>lag</sub>     | CLK low before NCS high (6)         | Application info | 100 |    | ns  |

|----------------------|-------------------------------------|------------------|-----|----|-----|

| T <sub>hclch</sub>   | CLK high after NCS high             | Application info | 100 |    | ns  |

| T <sub>onncs</sub>   | NCS min high time (9)               | Application info | 1   |    | us  |

| $T_{pchdz}$          | NCS L/H to SDO @ high impedance (E) | Cload=30pF       |     | 75 | ns  |

| F <sub>CLK_SPI</sub> | CLK frequency (50% duty cycle)      | Application info |     | 5  | MHz |

Figure 3. SPI timing diagram

## 7. Functional description

### 7.1. VM & VM UV / OV protection

VM is the supply voltage, range from 4.5v to 36v with typical case 13.5v power supply. It is recommended to put at both 100nF ceramic and >10uF bulk electrolytic capacitor closed to each VM pin.

When VM power supply pin voltage falls below the undervoltage threshold ( $V_{UV}$ ) over 10us typ. undervoltage deglitch time, half bridge outputs OUTx becomes OFF. When VM rise above the  $V_{UV}$ , the device automatically resumes operation.

When VM power supply pin voltage rises above the overvoltage threshold ( $V_{OV}$ ) over 10us typ. overvoltage deglitch time, half bridge outputs OUTx becomes OFF. When VM decrease under the  $V_{OV}$ , the device automatically resumes operation. OVP\_H register bit set the two different VM input overvoltage threshold.

### 7.2. VDD

VDD pin accepts wide supply range from 3v to max 5.5v which intends for the compatibility with both 3.3v and 5v system supply. 100nF X7R ceramic capacitor is suggested to put closed to VDD pin.

Internal block, SPI interface, digital block will be inactive when VDD drops below  $V_{VDD\_POR\_L}$ , so including charge pump and all half bridge drivers are switched off. Once VDD >  $V_{VDD\_POR\_H}$ , internal digital is reset, and status register NPOR bit is set to 0 and can be cleared to 1 by SPI readout (if RD CLR EN=1) or CLR FLT = 1 command.

### 7.3. EN input

The EN pin signal is common for all output channels. When it is driven low, internal logic / register is reset, charge pump / all outputs are disabled, and device enter sleep mode.

After EN transition from low to high at VDD > VVDD POR H, device come out sleep mode at finishing internal POR and NPOR=0.

A Twake time shall be wait for charge pump reach regulated voltage once device move from sleep to normal operation.

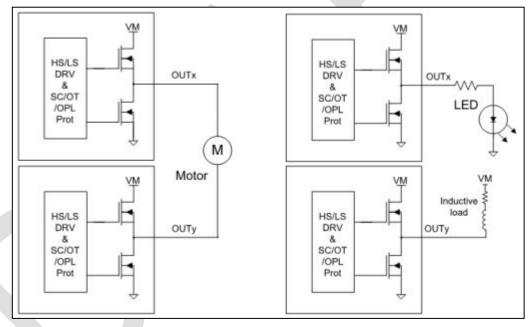

#### 7.4. Half bridge output stage, OUT1 ~ OUT8

The half bridge drivers are designed to drive DC motor or general used inductive/resistive load like LED.

The power stage outputs (out1~out12) can be in parallel to support higher load current.

Figure 4. Power stage output block diagram

### 7.4.1. SPI Control ON/OFF operation

To directly operate half bridge output by only SPI ON/OFF control, the two group register as below shall be controlled in following steps.

- 1. HBx PWM EN bit configuration in register HB PWM CTRL1 and FW PWM CTRL 2

- 2. HBx\_HS\_EN or HBx\_LS\_EN bit configuration in register HB\_CTRL1 / HB\_CTRL2 / CTRL3

Note:

- HBx\_PWM\_EN bit shall be configured or keep default value '0' for SPI control ON/OFF operation

- One specific half bridge, HBx\_HS\_EN and HBx\_LS\_EN shall not be '1' at the same time, otherwise, the specific half bridge will be HIZ until this same bridge HS and LS control bit both high condition is removed

Example of activation of HB1\_HS / HB1\_LS and HB2\_HS / HB2\_LS to drive motor by SPI control as table 2 shown

OUT2 EN HB1 register setting HB2 register setting OUT1 LOW HIZ HIZ Х High HB1 PWM EN=0 HB2 PWM EN=0 HIZ HIZ HB1 HS EN=0 HB2 HS EN=0 HB1 LS EN=0 HB2 LS EN=0 HB1\_PWM\_EN=0 HB2\_PWM\_EN=0 High High Low HB1\_HS\_EN=1 HB2\_HS\_EN=0 HB1\_LS\_EN=0 HB2\_LS\_EN=1 High HB1 PWM EN=0 HB2 PWM EN=0 Low Low HB1 HS EN=0 HB2 HS EN=0 HB1\_LS\_EN=1 HB2\_LS\_EN=1 High HB1 PWM EN=0 HB2 PWM EN=0 High Low HB1 HS EN=0 HB2 HS EN=1 HB1 LS EN=0 HB2 LS EN=0 HB1 PWM EN=0 HB2 PWM EN=0 High High High HB2\_HS\_EN=1 HB1\_HS\_EN=1 HB1 LS EN=0 HB2 LS EN=0

Table 2. Half bridge SPI control register setting example

#### 7.4.2. PWM control operation

PWM control is based on internal digital PWM generator and map control block. It is suggested to set following registers

- PWM frequency / duty cycle / map control

- (1) PWMx\_FREQ bit in PWM\_FREQ\_CTRL1 / PWM\_FREQ\_CTRL2 registers

Total 8 PWM generator, 2bit configuration for each PWM freq as (80Hz / 100Hz / 200Hz) in +/-30% variation for full operating and temperature range.

- (2) PWMx\_DUTY\_CYCLE bit in PWM\_DC\_CTRL1~PWM\_DC\_CTRL8 registers

8bit configuration of PWMx\_DUTY\_CYCLE define the duty cycle of generated PWMx as 100%\*BIT value /255

- (3) HBx\_PWM\_MAP bit in PWM\_MAP\_CTRL1~PWM\_MAP\_CTRL6 registers

3bit for each Half bridge, which allows independent and flexible selection from PWM1~PWM8

- Half bridge driver setting for PWM

- (1) HBx\_PWM\_EN bit in HB\_PWM\_CTRL1, FW\_PWM\_CTRL2

HBx\_PWM\_EN bit changed to '1' will enable the selected half bridge operation control by mapped PWM

- (2) HBx\_HS\_EN / HBx\_LS\_EN in HB\_CTRL1~HB\_CTRL3

Set HBx\_HS\_EN or HBx\_LS\_EN bit at '1' to enable the PWM activated Power FET stage.

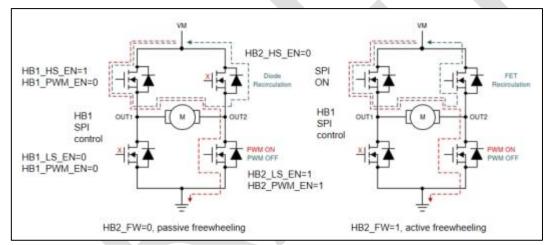

- Active / passive freewheeling setting in PWM

- (1) HBx\_FW bit in FW\_CTRL\_1, FW\_PWM\_CTRL\_2 registers

When the particular half bridge channel is chosen to use PWM, it is also possible to select the active or passive freewheeling option for the half bridge channel, by HBx FW control bit.

Example of active HB1 SPI ON and HB2 LS in PWM mode / HB2 HS in passive or active freewheeling to drive motor / inductive load

Figure 5. Passive freewheeling vs. active freewheeling

#### Note:

- Active freewheeling function automatically turns on the freewheeling FET, after the driving FET turns off at PWM ON->OFF and cross protection time  $t_{DEAD}$  elapsed

- HBx\_FW bit value is not effective when HBx\_PWM\_EN bit is configured as SPI control ON/OFF

- PWM enable / disable

- (1) PWMx\_DIS bit in HB\_PWM\_CTRL2

PWM channel independent enable / disable bit

Example of PWM mode control register setting and steps

- 1. Configure PWMx DIS bit into '1' (PWM stopped and off) for selected PWM channel

- 2. Configure active or passive free-wheeling in FW\_CTRL register

- 3. Assign the PWM channel for selected half-bridge output in PWM MAP CTRL register

- 4. Configure the PWM frequency in PWM\_FREQ\_CTRL register

- 5. Configure the PWM duty cycle in PWM DC CTRL register

- 6. Assign the channel driven mode SPI on/off or PWM operation by HBx\_PWM\_EN in HB\_PWM\_CTRL register

## **NSD8308**

- 7. Select the channel HS or LS to be driven by HBx HS EN or HBx LS EN in HB CTRL register

- 8. Active and begin the PWM by PWMx DIS bit to '0

#### 7.4.3. Output in parallel

For SPI ON/OFF control in parallel, it is recommended to select half bridge channel in same register, ie HB1, HB2, HB3, HB4 HS / LS control bit are all in HB\_CTRL\_1 register, while HB5, HB6, HB7, HB8 are in HB\_CTRL\_2.

For PWM control in parallel, to ensure the HS or LS activated simultaneously, it is mandatory to put the PWM activation in the last step for PWM mode control register setting.

#### 7.5. Half bridge protection and diagnosis

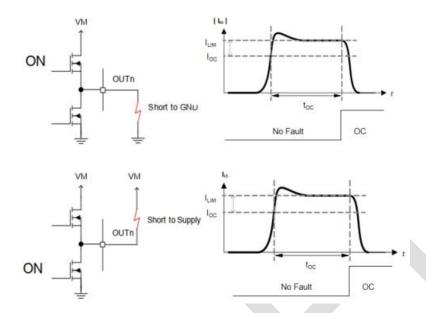

#### 7.5.1. Overcurrent protection

The integrated overcurrent protection function provides the half bridge high side against short to ground or half bridge low side against short to battery.

When the current pass the half bridge high side (VM->highside->OUTx) or flow into the half bridge low side (OUTx->low side->GND), once  $I_{OC}$  overcurrent threshold is exceeded, an overcurrent deglitch filter  $t_{OC}$  starts and internal circuit limits current at  $I_{LIM}$ .

Upon the overcurrent condition last until  $t_{OC}$  expiration, the particular half bridge (including high side and low side) are disabled. The OC status bit shall report the corresponding HS or LS which trigger OC. nFAULT pin also asserts low if OC\_MASK\_FLT is set '0'.

#### Note:

- 1. Even the half bridge output is disabled due to overcurrent protection mechanism, the HBx\_HS\_EN or HBx\_LS\_EN bit remains previous state, unless user change the value through SPI.

- 2. When device operate in high voltage up to 36v, short toc (OC\_Filter bit in OPL\_OC\_CTRL3 register) is suggested.

For example, if only HB1 LS is short to battery and detected, OC\_STA\_1 register HB1\_LS\_OC bit is asserted while HB1\_HS\_OC bit not affected, for output stage, both HB1 HS and LS are disabled.

To resume normal driving, besides the overcurrent condition disappear, it is also required to clear the OC status bit by SPI reading (RD\_CLR\_EN=1) or writing CLR\_FLT bit '1' to trigger clear fault command.

Anyhow if overcurrent condition short than  $t_{\text{OC}}$  deglitch filter, the OC event is not confirmed and HB driver keeps normal status.

The device also provides two slew rate options in case half bridge output stage turn off caused by OC protection. High slew rate turns off (typ 2.5v/us) used in default for OC as OC\_OFF\_SR bit in OPL\_OC\_CTRL\_3 is set to '0', while slow slew rate turns off in OC condition (OC\_OFF\_SR=1) shall be carefully evaluated for device operating ambient condition and power dissipation.

#### 7.5.2. Open load in ON state

The load current is monitored in each activated output stage for open load detection in ON state.

If the load current is below open load detection threshold  $I_{OL}$  for at least typ.2ms ( $t_{OL}$ ), the corresponding open load bit is set in status register.

The device also provide HBx\_OPL\_TH selection bit for lower open load threshold I<sub>OL\_LOW</sub> and the corresponding filter time t<sub>OL\_LOW</sub>, which targets for low current loads ie. LED.

Furthermore, two bits, OPL\_HB\_ACT bit and OPL\_mask\_FLT bit in OPL\_OC\_CTRL\_2 register, can be configured for open load fault reaction.

OPL\_HB\_ACT bit determines whether half bridge output status is impacted by ON state open load fault. Default value '0' will disable faulty half bridge HS and LS, while setting the bit value to '1' can choose open load only as information flag and half bridge control / operation not impacted.

OPL\_mask\_FLT bit determines whether nFault output pin status is impacted by ON state open load fault. Default value '0' unmasks and generates nFault low at open load detected, while changing to '1' will mask open load fault and doesn't report on nFault output.

User can clear the OL status bit by SPI reading (RD\_CLR\_EN=1) or writing CLR\_FLT bit '1' to trigger clear fault command to determine whether open load is still present or disappeared.

#### Note:

1. For DC motor application, it is recommended to use SPI ON/OFF short activation of outputs (e.g. 3ms) to test DC motor open load status without changing the mechanical state of motor.

2. For LED load application, PWM control might be used, the lower open load threshold and shorter filter shall be chosen. During PWM OFF/freewheeling state, open load detection is blanked.

Each half bridge ON state open load detection can be disabled by HBx\_OPL\_DIS bit in OPL\_CTRL\_1/2 register, in case ON state open load not required.

#### 7.5.3. OFF-state diagnosis

Each half bridge OUTx integrates internal pull up current / pull down current and comparator for off-state diagnosis.

Pull up current or pull down current are individually controlled as enable / disable by register OPL\_CTRL\_5 and OPL\_CTRL\_6 bit setting values.

The OUTx pin voltage is compared with VSTA\_HB to determine its off-state logic status (HIGH or LOW) in real time and reported in HB\_STA1 register.

#### Note:

Half bridge/H-bridge application connection is different with HS or LS usage. It is suggested to follow the following off-state diagnosis step including the pull up / down current enable/disable and OUTx status judgement through microcontroller.

#### 7.5.4. Overtemperature

To protect power stage from overheat, dedicated thermal sensor is placed close to each half bridge power stage, if the temperature increases above the OTwarn, a temperature warning flag is set in SPI STA\_0 register, half bridge output operation is not impacted. Once the sensed temperature over the second OT<sub>SD</sub> threshold, the corresponding OTSD flag is set and power MOSFET channel is automatically disabled.

nFAULT pin can be configured for OTwarn event report upon OTW\_MASK\_FLT bit setting. Anyhow OTSD will always asserted nFAULT to low.

OTwarn and OTSD flag bit are latched. In order to reactive the output stage after OTSD and release nFAULT pin, the temperature drops below T<sub>SD</sub>-T<sub>HYS</sub>, and the thermal shutdown OTSD bit shall be clear by SPI command.

#### 7.5.5. Fault Protection Summary

|                   |              | VM                    | 1        | VDD         | EN                                                                         | Therm                    | nal                            | Load cur                                          | rent                       |                 |

|-------------------|--------------|-----------------------|----------|-------------|----------------------------------------------------------------------------|--------------------------|--------------------------------|---------------------------------------------------|----------------------------|-----------------|

| EVENT             | OV1<br>t>tov | OV2<br>t>tov          | UV       | UV          | H->L                                                                       | OVER TEMPERATURE Warning | OVER<br>TEMPERATURE<br>shutdon | ОС                                                | OL in ON                   |                 |

|                   |              | _0 register<br>_H bit |          |             |                                                                            | OTW_MASK_FLT             |                                | OC_MASK_FLT                                       | OPL_HB_ACT<br>OPL_mask_FLT |                 |

| FLAG READ BY SPI  | VM_OV        | VM_OV                 | VM_M     | <u>(</u>    | Y<br>O<br>Z                                                                | OTWARN                   | OTSD                           | HBX_HB_OC<br>HBX_LS_OC                            | HBX_HS_OPL<br>HBX_LS_OPL   |                 |

| Internal supply   | 0            | 0                     | 0        | •           | •                                                                          | 0                        | 0                              | 0                                                 | 0                          |                 |

| Internal OSC      | 0            | 0                     | 0        | •           | •                                                                          | 0                        | 0                              | 0                                                 | 0                          |                 |

| Charge pump       | 0            | 0                     | <b>A</b> | •           | •                                                                          | 0                        | 0                              | 0                                                 | 0                          |                 |

| OUT1~OUT12        | <b>A</b>     | •                     | •        | •           | •                                                                          | 0                        | <b>A</b>                       | <b>▲</b> *1                                       | <b>▲</b> *2 *1             |                 |

| nFault            | Δ            | Δ                     | Δ        | -           | -                                                                          | Δ*3                      | Δ                              | △*4                                               | Δ*5                        |                 |

| SPI communication | 0            | 0                     | 0        | •           | •                                                                          | 0                        | 0                              | 0                                                 | 0                          |                 |

| SPI REGISTERS     | 0            | 0                     | 0        | •           | •                                                                          | 0                        | 0                              | 0                                                 | 0                          |                 |

|                   | detection    |                       | *1       | The fault o |                                                                            | hata a succed by OC a    | o Ol io ON io lo               | tched until the correst                           |                            | adition in most |

| <b>x</b><br>O     | normal ope   | rotion                | *2       |             |                                                                            |                          |                                | icried until the corresp<br>iel both HS and LS ou |                            |                 |

| -                 | not active   | auon                  | *3       |             |                                                                            |                          |                                | triggers nFAULT low                               |                            | ACT DIL =0.     |

| _                 | partial func | tionality             | *4       |             |                                                                            | unmasks and report       |                                |                                                   |                            |                 |

| Ă                 | stop/reset   | uonanty               | *5       |             |                                                                            |                          |                                |                                                   | od                         |                 |

| Δ                 | active LOW   |                       | υ        | OFL_IIIasi  | DPL_mask_FLT=0 unmasks and report on nFAULT if Open load on state detected |                          |                                |                                                   |                            |                 |

| Δ                 | active LOVV  |                       |          |             |                                                                            |                          |                                |                                                   |                            |                 |

#### 7.6. SPI interface

The following table summarizes the SPI interface designed.

Table 55 - SPI Interface quick look

| Parameter                 | Description        |

|---------------------------|--------------------|

| Protocol                  | in frame           |

| Single Frame Length       | 16 bit, MSB first  |

| Frame protection          | frame length check |

| Max. Frequency            | 5 MHz              |

| CPOL                      | 0                  |

| СРНА                      | 1                  |

| Master/Slave onfiguration | Slave              |

The falling edge of NCS defines the start of the SPI frames. It samples the SDI line at the falling edge of SCK, while the output data is shifted out on SDO line at the rising edge of SCK (CPOL='0' CPHA = '1'). The end of SPI frame is defined by a rising edge of NCS.

#### 7.6.1. Frame Length Check

For each command received, the SPI peripheral checks the number of clock edges at SCK pin. If the total number of edges is not a multiple of 16, the frame content is discarded and an SPI\_ERR bit will be returned upon next iteration.

#### 7.6.2. Error Frame

In case one of the following error occurs, the SPI ERR diagnosis bit will be returned upon next communication iteration:

- Frame Length error

- Invalid address

#### 7.6.3. SPI Frame structure

Each SDI input frame has 16 bits with the following structure:

- 2 operation command bit C1 / C0 '00' for write operation, '01' for read operation

- 6 ADDRESS bits

- 8 DATA bits

|     | MSB |    |      |      |      |      |      |      | LSB   |

|-----|-----|----|------|------|------|------|------|------|-------|

| BIT | 15  | 14 | 13   | 12   | 11   | 10   | 9    | 8    | [7:0] |

| SDI | C1  | СО | A[5] | A[4] | A[3] | A[2] | A[1] | A[0] | DATA  |

Register frame SDO responses the selected address and register content bit values. It has with the following structure:

- 2bit '1', reserved

- 6bits, UV event / OV event , Overtemperature, NPOR and power stage status OC, OL

- 8 DATA bits

|     | MSB |    |    |    |    |    |    |      | LSB   |

|-----|-----|----|----|----|----|----|----|------|-------|

| BIT | 15  | 14 | 13 | 12 | 11 | 10 | 9  | 8    | [7:0] |

| SDO | 1   | 1  | ОТ | OL | ос | UV | OV | NPOR | DATA  |

#### Note:

For SPI write operation, the SDO response data is the value which is currently written to.

For SPI read operation, the SDO response data is the value which register address has been read.

#### 7.6.4. Parallel and daisy chain capability

SPI communication between microcontroller (SPI master) and multiple these devices (slave) can be operated in parallel or in daisy chain.

Parallel operation: several slave devices are connected to one SPI channel, which share communication lines SDI, SDO and

SCK, but every slave connects dedicated own NCS.

Daisy chain operation: multi devices are connected with shared one NCS and SCK, while each device SDI and SDO are daisy-chain connected.

### 7.6.5. Registers map

| CECT                | DEC NAME       | REG_ |                      |            |                             | bi          | its         |                   |             |            |

|---------------------|----------------|------|----------------------|------------|-----------------------------|-------------|-------------|-------------------|-------------|------------|

| SECT                | REG_NAME       | ADDR | D7                   | D6         | D5                          | D4          | D3          | D2                | D1          | D0         |

|                     | <u>STA_0</u>   | 0x00 | Reserved             | OTSD       | OTWARN                      | OPL         | ОС          | VM_UV             | VM_OV       | NPOR       |

|                     | OC STA 1       | 0x01 | HB4_HS_OC            | HB4_LS_OC  | HB3_HS_OC                   | HB3_LS_OC   | HB2_HS_OC   | HB2_LS_OC         | HB1_HS_OC   | HB1_LS_OC  |

|                     | OC_STA_2       | 0x02 | HB8_HS_OC            | HB8_LS_OC  | HB7_HS_OC                   | HB7_LS_OC   | HB6_HS_OC   | HB6_LS_OC         | HB5_HS_OC   | HB5_LS_OC  |

|                     | OC STA 3       | 0x03 |                      |            |                             | Reve        | ersed       |                   |             |            |

| Status<br>registers | OPL STA 1      | 0x04 | HB4_HS_OPL           | HB4_LS_OPL | HB3_HS_OPL                  | HB3_LS_OPL  | HB2_HS_OPL  | HB2_LS_OPL        | HB1_HS_OPL  | HB1_LS_OPL |

|                     | OPL STA 2      | 0x05 | HB8_HS_OPL           | HB8_LS_OPL | HB7_HS_OPL                  | HB7_LS_OPL  | HB6_HS_OPL  | HB6_LS_OPL        | HB5_HS_OPL  | HB5_LS_OPL |

|                     | OPL STA 3      | 0x06 |                      |            |                             | Reve        | ersed       |                   |             |            |

|                     | HB STA 1       | 0x2B | HB8_STA              | HB7_STA    | HB6_STA                     | HB5_STA     | HB4_STA     | HB3_STA           | HB2_STA     | HB1_STA    |

|                     | HB STA 2       | 0x2C |                      |            |                             | Reve        | ersed       |                   |             |            |

|                     | GEN_CTRL_0     | 0x07 | OFF_DIAG_CO<br>MP_EN |            | DEVICE_ID                   |             | OC_MASK_FLT | OTW_NMASK_<br>FLT | OVP_H       | DIAG_CLR   |

|                     | HB_CTRL_1      | 0x08 | HB4_HS_EN            | HB4_LS_EN  | HB3_HS_EN                   | HB3_LS_EN   | HB2_HS_EN   | HB2_LS_EN         | HB1_HS_EN   | HB1_LS_EN  |

|                     | HB CTRL 2      | 0x09 | HB8_HS_EN            | HB8_LS_EN  | HB7_HS_EN                   | HB7_LS_EN   | HB6_HS_EN   | HB6_LS_EN         | HB5_HS_EN   | HB5_LS_EN  |

|                     | HB_CTRL_3      | 0x0A |                      |            |                             | Reversed    |             |                   |             |            |

|                     | HB_PWM_CTRL1   | 0x0B | HB8_PWM_EN           | HB7_PWM_EN | HB6_PWM_EN                  | HB5_PWM_EN  | HB4_PWM_EN  | HB3_PWM_EN        | HB2_PWM_EN  | HB1_PWM_EN |

|                     | HB PWM CTRL2   | 0x0C | PWM8_DIS             | PWM7_DIS   | PWM6_DIS                    | PWM5_DIS    | PWM4_DIS    | PWM3_DIS          | PWM2_DIS    | PWM1_DIS   |

| Control             | FW_CTRL_1      | 0x0D | HB8_FW               | HB7_FW     | HB6_FW                      | HB5_FW      | HB4_FW      | HB3_FW            | HB2_FW      | HB1_FW     |

| registers           | FW_PWM_CTRL_2  | 0x0E |                      |            |                             | Reve        | ersed       |                   |             |            |

|                     | PWM MAP CTRL 1 | 0x0F | Reserved             | Reserved   |                             | HB2_PWM_MAP |             |                   | HB1_PWM_MAP |            |

|                     | PWM_MAP_CTRL_2 | 0x10 | Reserved             | Reserved   |                             | HB4_PWM_MAP |             |                   | HB3_PWM_MAP |            |

|                     | PWM_MAP_CTRL_3 | 0x11 | Reserved             | Reserved   | HB6_PWM_MAP HB5_PWM_MAP     |             |             |                   |             |            |

|                     | PWM MAP CTRL 4 | 0x12 | Reserved             | Reserved   | red HB8_PWM_MAP HB7_PWM_MAP |             |             |                   |             |            |

|                     | PWM FREQ CTRL1 | 0x13 | PWM4                 | _FREQ      | PWM3_FREQ PWM2_FREQ         |             |             |                   |             | _FREQ      |

|                     | PWM_FREQ_CTRL2 | 0x14 | PWM8                 | _FREQ      | PWM7                        | _FREQ       | PWM6        | 5_FREQ            | PWM5_FREQ   |            |

| L | PWM DC CTRL1   | 0x15 |                                                     |                             |                   | PWM1_DU           | JTY_CYCLE         |                   |                   |                   |  |  |  |  |  |

|---|----------------|------|-----------------------------------------------------|-----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--|--|--|--|--|

|   | PWM_DC_CTRL2   | 0x16 |                                                     |                             |                   | PWM2_DI           | JTY_CYCLE         |                   |                   |                   |  |  |  |  |  |

|   | PWM_DC_CTRL3   | 0x17 |                                                     | PWM3_DUTY_CYCLE             |                   |                   |                   |                   |                   |                   |  |  |  |  |  |

|   | PWM_DC_CTRL4   | 0x18 |                                                     | PWM4_DUTY_CYCLE             |                   |                   |                   |                   |                   |                   |  |  |  |  |  |

|   | PWM_DC_CTRL5   | 0x19 |                                                     |                             |                   | PWM5_DI           | JTY_CYCLE         |                   |                   |                   |  |  |  |  |  |

|   | PWM DC CTRL6   | 0x1A |                                                     |                             |                   | PWM6_DI           | JTY_CYCLE         |                   |                   |                   |  |  |  |  |  |

| f | PWM DC CTRL7   | 0x1B |                                                     |                             |                   | PWM7_DI           | JTY_CYCLE         |                   |                   |                   |  |  |  |  |  |

| l | PWM DC CTRL8   | 0x1C |                                                     |                             |                   | PWM8_DI           | JTY_CYCLE         |                   |                   |                   |  |  |  |  |  |

| Ī | HB SR CTRL 1   | 0x1D | HB8_SR                                              | HB7_SR                      | HB6_SR            | HB5_SR            | HB4_SR            | HB3_SR            | HB2_SR            | HB1_SR            |  |  |  |  |  |

| Ī | HB SR CTRL 2   | 0x1E |                                                     |                             |                   | Reve              | ersed             |                   |                   |                   |  |  |  |  |  |

|   | OPL_CTRL_1     | 0x1F | HB8_OPL_DIS                                         | HB7_OPL_DIS                 | HB6_OPL_DIS       | HB5_OPL_DIS       | HB4_OPL_DIS       | HB3_OPL_DIS       | HB2_OPL_DIS       | HB1_OPL_DIS       |  |  |  |  |  |

|   | OPL OC CTRL 2  | 0x20 | OPL_mask_FLT OPL_HB_ACT Reserved OC_OFF_SR reversed |                             |                   |                   |                   |                   |                   |                   |  |  |  |  |  |

|   | OPL OC CTRL 3  | 0x21 |                                                     | OC_FILTER Reserved reversed |                   |                   |                   |                   |                   |                   |  |  |  |  |  |

|   | OPL_CTRL_4     | 0x22 | HB8_OPL_TH                                          | HB7_OPL_TH                  | HB6_OPL_TH        | HB5_OPL_TH        | HB4_OPL_TH        | HB3_OPL_TH        | HB2_OPL_TH        | HB1_OPL_TH        |  |  |  |  |  |

|   | OPL_CTRL_5     | 0x23 |                                                     |                             |                   | Reve              | ersed             |                   |                   |                   |  |  |  |  |  |

|   | OPL CTRL 6     | 0x24 |                                                     |                             |                   | Reversed          |                   |                   |                   |                   |  |  |  |  |  |

|   | GEN_CTRL_1     | 0x25 | SS_M                                                | MOD                         | SS_DEV            | RD_CLR_EN         | unlock            | SPI_ERR           | Device            | e_VER             |  |  |  |  |  |

|   | PWM MAP CTRL 5 | 0x26 |                                                     |                             |                   | Reve              | ersed             |                   |                   |                   |  |  |  |  |  |

|   | PWM MAP CTRL 6 | 0x27 |                                                     |                             |                   | Reve              | ersed             |                   |                   |                   |  |  |  |  |  |

|   | OPL CTRL 5     | 0x28 | HB4_OFF_PU_<br>EN                                   | HB4_OFF_PD_<br>EN           | HB3_OFF_PU_<br>EN | HB3_OFF_PD_<br>EN | HB2_OFF_PU_<br>EN | HB2_OFF_PD_<br>EN | HB1_OFF_PU_<br>EN | HB1_OFF_PD_<br>EN |  |  |  |  |  |

|   | OPL CTRL 6     | 0x29 | HB8_OFF_PU_                                         | HB8_OFF_PD_                 | HB7_OFF_PU_       | HB7_OFF_PD_       | HB6_OFF_PU_       | HB6_OFF_PD_       | HB5_OFF_PU_       | HB5_OFF_PD_       |  |  |  |  |  |

| ŀ | OPL CTRL 7     | 0x2A | EN                                                  | EN                          | EN                | EN                | EN EN ersed       | EN                | EN                | EN                |  |  |  |  |  |

| ŀ |                |      | HB8_IPUPD_M                                         | HB7_IPUPD_M                 | HB6_IPUPD_M       | HB5_IPUPD_M       | HB4_IPUPD_M       | HB3_IPUPD_M       | HB2_IPUPD_M       | HB1_IPUPD_M       |  |  |  |  |  |

| Ĺ | OPL CTRL 8     | 0x2D | ODE                                                 | ODE                         | ODE ODE           | ODE               | ODE               | ODE ODE           | ODE ODE           | ODE               |  |  |  |  |  |

|   | OPL_CTRL_9     | 0x2E | OCPH_CONF                                           | VM_OVPH_CO<br>NF            | IDCH_CONF         | TDEAD_MON_<br>EN  |                   | Reve              | ersed             |                   |  |  |  |  |  |

| Register<br>Name | Addre<br>ss | Field Name | Туре | Bit<br>Offset | Bit<br>Width | Reset<br>Value | Description                                                                                                                                           |

|------------------|-------------|------------|------|---------------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| STA_0            | 0x0         |            |      |               |              |                |                                                                                                                                                       |

|                  |             | Reserved   | RO   | 7             | 1            | 0x0            | 0: reversed (default value).                                                                                                                          |

|                  |             | OTSD       | RLR  | 6             | 1            | 0x0            | O: No over temperature shutdown happen (default value) 1: over temperature shutdown detected. Error latched and all outputs disabled.                 |

|                  |             | OTWARN     | RLR  | 5             | 1            | 0x0            | O: No over temperature warning happen (default value) 1: over temperature warning detected.                                                           |

|                  |             | OPL        | RO   | 4             | 1            | 0x0            | 0: No open load detected (default value) 1: open load detected in at least one of power stages.                                                       |

|                  |             | ос         | RO   | 3             | 1            | 0x0            | O: No overcurrent detected (default value) 1: overcurrent detected in at least one of power stages. Error latched and corresponding outputs disabled. |

|                  |             | VM_UV      | RLR  | 2             | 1            | 0x0            | O: No VM undervoltage detected (default value) 1: VM undervoltage detected. Error latched and all outputs disabled.                                   |

|                  |             | VM_OV      | RLR  | 1             | 1            | 0x0            | O: No VM overvoltage detected (default value) 1: VM overvoltage detected. Error latched and all outputs disabled.                                     |

|                  |             | NPOR       | RLR  | 0             | 1            | 0x0            | 0: POR due to VDD supply or EN (default value) 1: No POR                                                                                              |

| OC_STA_1         | 0x1         |            |      |               |              |                |                                                                                                                                                       |

|                  |             | HB4_HS_OC  | RLR  | 7             | 1            | 0x0            | O: No overcurrent in HB4 high side detected (default value) 1: overcurrent detected in HB4 high side. Error latched, HB4 HS is disabled.              |

|                  |             | HB4_LS_OC  | RLR  | 6             | 1            | 0x0            | O: No overcurrent in HB4 low side detected (default value) 1: overcurrent detected in HB4 low side. Error latched, HB4 LS is disabled.                |

|                  |             | HB3_HS_OC  | RLR  | 5             | 1            | 0x0            | O: No overcurrent in HB3 high side detected (default value) 1: overcurrent detected in HB3 high side. Error latched, HB3 HS is disabled.              |

|                  |             | HB3_LS_OC  | RLR  | 4             | 1            | 0x0            | O: No overcurrent in HB3 low side detected (default value) 1: overcurrent detected in HB3 low side. Error latched, HB3 LS is disabled.                |

|                  |             | HB2_HS_OC  | RLR  | 3             | 1            | 0x0            | O: No overcurrent in HB2 high side detected (default value) 1: overcurrent detected in HB2 high side. Error latched, HB2 HS is disabled.              |

|                  |             | HB2_LS_OC  | RLR  | 2             | 1            | 0x0            | O: No overcurrent in HB2 low side detected (default value)  1: overcurrent detected in HB2 low side. Error latched, HB2 LS is disabled.               |

|                  |             | HB1_HS_OC  | RLR  | 1             | 1            | 0x0            | O: No overcurrent in HB1 high side detected (default value)  1: overcurrent detected in HB1 high side. Error latched, HB1 HS is disabled.             |

|          |     | HB1_LS_OC  | RLR | 0 | 1 | 0x0 | O: No overcurrent in HB1 low side detected (default value)  1: overcurrent detected in HB1 low side . Error                                   |

|----------|-----|------------|-----|---|---|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

| OC_STA_2 | 0x2 |            |     |   |   |     | latched, HB1 LS is disabled.                                                                                                                  |

| 0C_31A_2 | UXZ | HB8_HS_OC  | RLR | 7 | 1 | 0x0 | O: No overcurrent in HB8 high side detected (default value) 1: overcurrent detected in HB8 high side . Error latched, HB8 HS is disabled.     |

|          |     | HB8_LS_OC  | RLR | 6 | 1 | 0x0 | O: No overcurrent in HB8 low side detected (default value) 1: overcurrent detected in HB8 low side . Error latched, HB8 LS is disabled.       |

|          |     | HB7_HS_OC  | RLR | 5 | 1 | 0x0 | O: No overcurrent in HB7 high side detected (default value)  1: overcurrent detected in HB7 high side . Error latched, HB7 HS is disabled.    |

|          |     | HB7_LS_OC  | RLR | 4 | 1 | 0x0 | O: No overcurrent in HB7 low side detected (default value)  1: overcurrent detected in HB7 low side . Error latched, HB7 LS is disabled.      |

|          |     | HB6_HS_OC  | RLR | 3 | 1 | 0x0 | O: No overcurrent in HB6 high side detected (default value) 1: overcurrent detected in HB6 high side . Error latched, HB6 HS is disabled.     |

|          |     | HB6_LS_OC  | RLR | 2 | 1 | 0x0 | O: No overcurrent in HB6 low side detected (default value)  1: overcurrent detected in HB6 low side . Error latched, HB6 LS is disabled.      |

|          |     | HB5_HS_OC  | RLR | 1 | 1 | 0x0 | O: No overcurrent in HB5 high side detected (default value) 1: overcurrent detected in HB5 high side . Error latched, HB5 HS is disabled.     |

|          |     | HB5_LS_OC  | RLR | 0 | 1 | 0x0 | O: No overcurrent in HB5 low side detected (default value)  1: overcurrent detected in HB5 low side . Error latched, HB5 LS is disabled.      |

| OC_STA_3 | 0x3 |            |     |   |   |     | ,                                                                                                                                             |

|          |     | HB12_HS_OC | RLR | 7 | 1 | 0x0 | O: No overcurrent in HB12 high side detected (default value) 1: overcurrent detected in HB12 high side . Error latched, HB12 HS is disabled.  |

|          |     | HB12_LS_OC | RLR | 6 | 1 | 0x0 | O: No overcurrent in HB12 low side detected (default value) 1: overcurrent detected in HB12 low side . Error latched, HB12 LS is disabled.    |

|          |     | HB11_HS_OC | RLR | 5 | 1 | 0x0 | O: No overcurrent in HB11 high side detected (default value)  1: overcurrent detected in HB11 high side . Error latched, HB11 HS is disabled. |

|          |     | HB11_LS_OC | RLR | 4 | 1 | 0x0 | 0: No overcurrent in HB11 low side detected (default value) 1: overcurrent detected in HB11 low side . Error latched, HB11 LS is disabled.    |

|          |     | HB10_HS_OC | RLR | 3 | 1 | 0x0 | 0: No overcurrent in HB10 high side detected (default value)                                                                                  |

|           |     |             | 1   | 1 | 1 | 1    | A                                                                                                                                                                     |

|-----------|-----|-------------|-----|---|---|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |     |             |     |   |   |      | 1: overcurrent detected in HB10 high side . Error                                                                                                                     |

|           |     |             |     |   |   |      | latched, HB10 HS is disabled.                                                                                                                                         |

|           |     | HB10 LS OC  | RLR | 2 | 1 | 0x0  | 0: No overcurrent in HB10 low side detected (default value)                                                                                                           |

|           |     | 11810_L3_OC | KLK | 2 | 1 | 0.00 | 1: overcurrent detected in HB10 low side . Error latched, HB10 LS is disabled.                                                                                        |

|           |     | HB9_HS_OC   | RLR | 1 | 1 | 0x0  | O: No overcurrent in HB9 high side detected (default value) 1: overcurrent detected in HB9 high side . Error latched, HB9 HS is disabled.                             |

|           |     | HB9_LS_OC   | RLR | 0 | 1 | 0x0  | O: No overcurrent in HB9 low side detected (default value) 1: overcurrent detected in HB9 low side . Error latched, HB9 LS is disabled.                               |

| OPL_STA_1 | 0x4 |             |     |   |   |      |                                                                                                                                                                       |

| 1         |     | HB4_HS_OPL  | RLR | 7 | 1 | 0x0  | O: No open load in HB4 high side detected (default value) 1: open load detected in HB4 high side . Error latched                                                      |

|           |     | HB4_LS_OPL  | RLR | 6 | 1 | 0x0  | O: No open load in HB4 low side detected (default value)  1: open load detected in HB4 low side . Error latched                                                       |

|           |     | HB3_HS_OPL  | RLR | 5 | 1 | 0x0  | 0: No open load in HB3 high side detected (default value) 1: open load detected in HB3 high side . Error latched                                                      |

|           |     | HB3_LS_OPL  | RLR | 4 | 1 | 0x0  | 0: No open load in HB3 low side detected (default value) 1: open load detected in HB3 low side . Error latched                                                        |

|           |     | HB2_HS_OPL  | RLR | 3 | 1 | 0x0  | 0: No open load in HB2 high side detected (default value) 1: open load detected in HB2 high side . Error latched                                                      |

|           |     | HB2_LS_OPL  | RLR | 2 | 1 | 0x0  | 0: No open load in HB2 low side detected (default value) 1: open load detected in HB2 low side . Error latched                                                        |

|           |     | HB1_HS_OPL  | RLR | 1 | 1 | 0x0  | O: No open load in HB1 high side detected (default value)  1: open load detected in HB1 high side . Error latched  O: No open load in HB1 low side detected (default) |

|           |     | HB1_LS_OPL  | RLR | 0 | 1 | 0x0  | 0: No open load in HB1 low side detected (default value) 1: open load detected in HB1 low side . Error latched                                                        |

| OPL_STA_2 | 0x5 |             |     |   |   |      |                                                                                                                                                                       |

|           |     | HB8_HS_OPL  | RLR | 7 | 1 | 0x0  | O: No open load in HB8 high side detected (default value)  1: open load detected in HB8 high side . Error latched                                                     |

|           |     | HB8_LS_OPL  | RLR | 6 | 1 | 0x0  | O: No open load in HB8 low side detected (default value) 1: open load detected in HB8 low side . Error latched                                                        |

|           |     | HB7_HS_OPL  | RLR | 5 | 1 | 0x0  | 0: No open load in HB7 high side detected (default value) 1: open load detected in HB7 high side . Error latched                                                      |

|           |     | HB7_LS_OPL  | RLR | 4 | 1 | 0x0  | 0: No open load in HB7 low side detected (default value) 1: open load detected in HB7 low side . Error latched                                                        |

|           |     | HB6_HS_OPL  | RLR | 3 | 1 | 0x0  | O: No open load in HB6 high side detected (default value)  1: open load detected in HB6 high side . Error latched                                                     |

|      | HB6_LS_OPL  | RLR        | 2                | 1                | 0x0                  | O: No open load in HB6 low side detected (default value) 1: open load detected in HB6 low side . Error latched                                                                |

|------|-------------|------------|------------------|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | HB5_HS_OPL  | RLR        | 1                | 1                | 0x0                  | 0: No open load in HB5 high side detected (default value)                                                                                                                     |

|      | HB5_LS_OPL  | RLR        | 0                | 1                | 0x0                  | 1: open load detected in HB5 high side . Error latched     0: No open load in HB5 low side detected (default value)                                                           |

|      |             |            |                  |                  |                      | 1: open load detected in HB5 low side . Error latched                                                                                                                         |

| 0x6  |             |            |                  |                  |                      |                                                                                                                                                                               |

|      | HB12_HS_OPL | RLR        | 7                | 1                | 0x0                  | O: No open load in HB12 high side detected (default value) 1: open load detected in HB12 high side . Error latched                                                            |