# 3V-40V, Low $I_{\text{Q}}$ , LDO with Watchdog and $V_{\text{BAT}}$ Sense

### 1 Features

- Automotive AEC-Q100 Grade 1 Qualified

- Functional Safety Ready

- Provide Functional Safety documentations to support system level functional safety design.

- Internal Safety Mechanisms are ready to be used in safety applications.

- LDO Function

- Wide Input Voltage Range: 3V to 40V

- Fixed 3.3V/5V Output Voltage, ±2% Accuracy

- Up to 300mA Output Current

- Low Operation I<sub>Q</sub>: 16μA

- Low Shutdown I<sub>SHDN</sub>: 1.5μA

- High PSRR 60dB @ 100Hz

- Accurate EN control

- Watchdog Function

- Window Watchdog

- Adjustable Watchdog Timer

- V<sub>BAT</sub> Sense Function

- VBAT UVLO: Open Drain Output

- V<sub>BAT</sub> Sense: Analog Output to ADC

- Dedicated BEN Pin to Minimize System IQ

- Protection Function

- ➢ V<sub>OUT</sub> OV/UV Detection

- Thermal Shutdown and Auto Restart

- Over-Current Protection

- Device Operating: –40°C to + 150°C

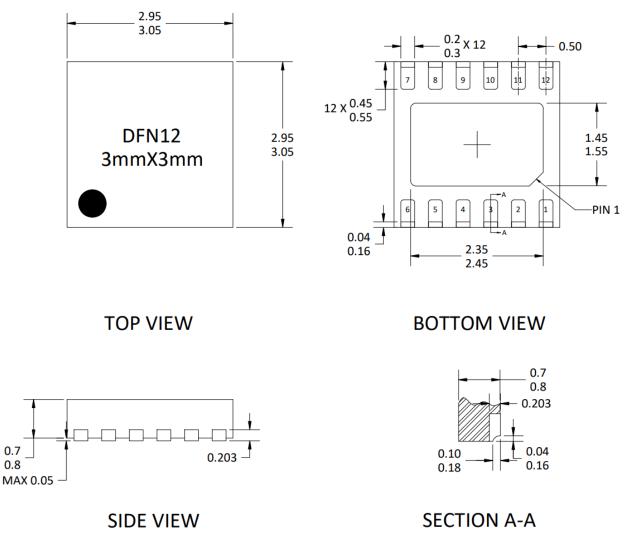

- DFN12(3X3) Package with Wettable Flanks

### 2 Applications

- In-Vehicle Infotainment (IVI)

- Body Control Module (Body)

- > ADAS

- Powertrain

### 3 Description

LN22043Q1 is a low quiescent current watchdog LDO with a wide input voltage range of 3V to 40V. The series provides 3.3V, 5V fixed outputs and delivers up to 300mA output current. Typical shutdown current of LN22043Q1 is less than  $1.5\mu$ A, while the quiescent current under no-load condition is  $16\mu$ A.

Watchdog function can provide an independent monitor for microcontrollers. Window watchdog mode can monitor whether the frequency of watchdog service signal (WDI) is within a preset range. Different fault conditions of missing pulse in open window and receiving pulse in close window can both be reported on RESET pin. The duration of watchdog window can be set by delay capacitor.

LN22043Q1 provides a battery voltage sense function. By integrating an independent switch and a dedicated BEN pin, V<sub>BAT</sub> sense function can be achieved by a minimum of peripheral circuit, without sacrificing system quiescent consumption.

LN22043Q1 also features power good indicator, over current protection and over temperature shutdown with auto restart. The product family are available in DFN12(3X3) package with wettable flanks.

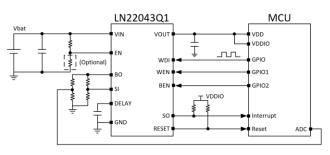

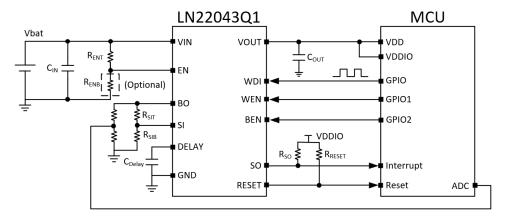

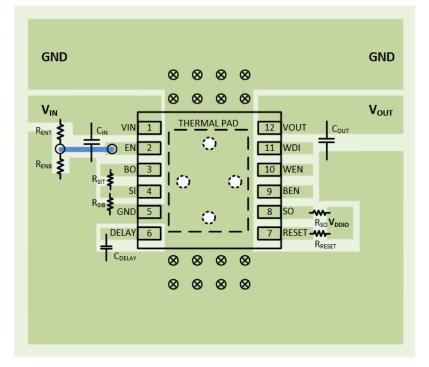

**Typical Application**

### **Table of Contents**

| Fea   | tures                                                                                                                                                                                               | 1                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Арр   | lications                                                                                                                                                                                           | 1                                 |

| Des   | cription                                                                                                                                                                                            | 1                                 |

| Ver   | sion History                                                                                                                                                                                        | 3                                 |

| Ord   | er Information                                                                                                                                                                                      | 4                                 |

| Pin   | Configuration and Function                                                                                                                                                                          | 5                                 |

| .1    | Pin Configuration                                                                                                                                                                                   | 5                                 |

| .2    | Pin Function                                                                                                                                                                                        | 5                                 |

| Spe   | cifications                                                                                                                                                                                         | 6                                 |

| .1    | Absolute Maximum Ratings                                                                                                                                                                            | 6                                 |

| .2    | ESD Ratings                                                                                                                                                                                         | 6                                 |

| .3    | Recommended Operating Condition                                                                                                                                                                     | 7                                 |

| .4    | Package Thermal Parameters                                                                                                                                                                          | 7                                 |

| .5    | Electrical Characteristics                                                                                                                                                                          | 8                                 |

| .6    | Typical Characteristics                                                                                                                                                                             | 11                                |

| Fun   | ctional Description                                                                                                                                                                                 | 16                                |

| .1    | Overview                                                                                                                                                                                            | 16                                |

| .2    | Funtional Dragram                                                                                                                                                                                   | 16                                |

| .3    | Funtional Description                                                                                                                                                                               | 17                                |

| Тур   | ical Applications                                                                                                                                                                                   | 22                                |

| .1    | Applicaition Diagram with Full Features                                                                                                                                                             | 22                                |

| .2    | Design Requirements                                                                                                                                                                                 | 22                                |

| .3    | Detailed Design Procedure                                                                                                                                                                           | 22                                |

| Layo  | out                                                                                                                                                                                                 | 25                                |

| 0.1   | Layout Guidelines                                                                                                                                                                                   | 25                                |

| 0.2   | Layout Example                                                                                                                                                                                      | 26                                |

| Pac   | kage Information                                                                                                                                                                                    | 27                                |

| 1.1   | Package Outline                                                                                                                                                                                     | 27                                |

| 1.2   | Footprint Example                                                                                                                                                                                   | 28                                |

| 1.3   | Tape and Reel Information                                                                                                                                                                           | 29                                |

| ortar | nt Notice and Disclaimers                                                                                                                                                                           | 30                                |

| irom  | ental Declaration                                                                                                                                                                                   | 30                                |

|       | App<br>Des<br>Ver:<br>Ord<br>Pin<br>.1<br>.2<br>.3<br>.4<br>.5<br>.6<br>Fun<br>.1<br>.2<br>.3<br>.4<br>.5<br>.6<br>Fun<br>.1<br>.2<br>.3<br>Layo<br>0.1<br>0.2<br>Pac<br>1.1<br>1.2<br>1.3<br>ortar | 2  Pin Function    Specifications |

# 4 Version History

| Version | Description     | Date      |

|---------|-----------------|-----------|

| 1.0     | Initial Version | 2024/5/20 |

|         |                 |           |

|         |                 |           |

|         |                 |           |

|         |                 |           |

### **5** Order Information

| Part Number    | Vout | Max<br>Load | Watchdog | V <sub>BAT</sub><br>Sense | PG  | IC Package | MSL-Peak-<br>Temp <sup>(1)</sup> | Material | Package<br>Qty      | Top<br>Marking <sup>(2)</sup> |

|----------------|------|-------------|----------|---------------------------|-----|------------|----------------------------------|----------|---------------------|-------------------------------|

| LN220433AQ1CHR | 3.3V | 300mA       | Window   | Yes                       | Yes | DFN12(3X3) | Level-2- 260C                    | RoHS     | Tape & Reel<br>3000 | 20433A                        |

| LN220435AQ1CHR | 5V   | 300mA       | Window   | Yes                       | Yes | DFN12(3X3) | Level-2- 260C                    | RoHS     | Tape & Reel<br>3000 | 20435A                        |

(1) MSL (Moisture Sensitivity Level) is based on JEDEC industrial classification and the tabled temperature is the maximum solder temperature.

(2) There may be additional marking related to the internal trace code on the device.

### 6 Pin Configuration and Function

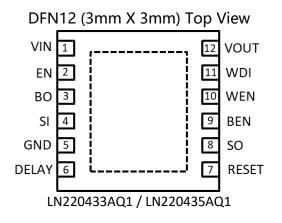

### 6.1 Pin Configuration

### 6.2 Pin Function

| Name  | Number | Description                                                                                                                                                                                                                                              |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN   | 1      | Input pin, place a ceramic capacitor of at least 1µF between VIN and GND.                                                                                                                                                                                |

| EN    | 2      | Enable pin, connect to a logic control signal or to VIN directly. This pin is pulled down to GND through internal resistor.                                                                                                                              |

| BO    | 3      | Battery voltage analog output (controlled by BEN).                                                                                                                                                                                                       |

| SI    | 4      | Battery voltage sense input. SO is pulled down when $V_{SI}$ falls below the sense-low threshold. If not used, connect to the BO pin.                                                                                                                    |

| GND   | 5      | Connect to GND.                                                                                                                                                                                                                                          |

| DELAY | 6      | Connected to an external delay capacitor. Set power good delay time and watchdog period.                                                                                                                                                                 |

| RESET | 7      | V <sub>OUT</sub> power good signal output and watchdog timeout reset signal output. Open drain, connect a pull-up resistor between RESET and an external power supply <sup>(1)</sup> or to VOUT pin, if not used, left this pin floating is recommended. |

| so    | 8      | Battery voltage sense output. Open drain, connect a pull-up resistor between SO and an external power supply <sup>(1)</sup> or to VOUT pin, if not used, left this pin floating is recommended.                                                          |

| BEN   | 9      | $V_{BAT}$ sense function enable. This pin is pulled down to GND through internal resistor.                                                                                                                                                               |

| WEN   | 10     | Watchdog function enable. This pin is pulled down to GND through internal resistor.                                                                                                                                                                      |

| WDI   | 11     | Watchdog signal input.                                                                                                                                                                                                                                   |

| VOUT  | 12     | Output pin, place a ceramic capacitor of at least 0.47µF between VOUT and GND.                                                                                                                                                                           |

(1) The external power supply voltage should not exceed  $V_{OUT}$ .

### 7 Specifications

### 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| Parameters                                                                                    | Min  | Max             | Unit |

|-----------------------------------------------------------------------------------------------|------|-----------------|------|

| V <sub>IN</sub>                                                                               | -0.3 | 42              |      |

| V <sub>EN</sub> / V <sub>SI</sub> / V <sub>BO</sub>                                           | -0.3 | V <sub>IN</sub> |      |

| V <sub>RESET</sub> / V <sub>WEN</sub> / V <sub>WDI</sub> / V <sub>BEN</sub> / V <sub>SO</sub> | -0.3 | 6.5             | V    |

| V <sub>OUT</sub>                                                                              | -0.3 | 6.5             |      |

| V <sub>DELAY</sub>                                                                            | -0.3 | 6.5             |      |

| Operating Junction Temperature                                                                | -40  | 150             |      |

| Operating Ambient Temperature                                                                 | -40  | 125             | °C   |

| Storage Temperature                                                                           | -55  | 150             |      |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                                               |                                                           | Value                                                    | Unit  |  |

|-----------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|-------|--|

|                                               |                                                           | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup>  | ±2000 |  |

| V <sub>(ESD)</sub> Electrostatic<br>discharge | Charged-device model (CDM), per AEC Q100-011, corner pins | ±750                                                     | V     |  |

|                                               |                                                           | Charged-device model (CDM), per AEC Q100-011, other pins | ±500  |  |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Condition

Over operating free-air temperature range (unless otherwise noted)

|                                                        | Parameters                      | Min  | Nom   | Max              | Unit |

|--------------------------------------------------------|---------------------------------|------|-------|------------------|------|

| V <sub>IN</sub>                                        | Input voltage                   | 3    |       | 40               |      |

| V <sub>OUT</sub>                                       | Output voltage                  |      | 3.3/5 |                  |      |

| V <sub>EN</sub> / V <sub>SI</sub> / V <sub>BO</sub>    | EN/SI/BO voltage                | 0    |       | V <sub>IN</sub>  | V    |

| V <sub>WEN</sub> / V <sub>WDI</sub> / V <sub>BEN</sub> | WEN/WDI/BEN voltage             | 0    |       | 5.5              | -    |

| V <sub>RESET</sub> / V <sub>SO</sub>                   | RESET/SO voltage                | 0    |       | V <sub>OUT</sub> |      |

| Iout                                                   | Output current                  | 0    |       | 300              | mA   |

| C <sub>IN</sub>                                        | Input capacitor                 | 1    |       |                  | - uF |

| C <sub>OUT</sub>                                       | Output capacitor <sup>(1)</sup> | 0.47 |       | 200              |      |

| T <sub>A</sub>                                         | Operating Ambient Temperature   | -40  |       | 125              | °C   |

| TJ                                                     | Operating Junction Temperature  | -40  |       | 150              |      |

(1) Consider the decrease of voltage and temperature, minimum effective capacitance of 0.47µF is required for stability.

### 7.4 Package Thermal Parameters

|                                                                       | Parameter                                        | DFN12(3X3) | Unit |

|-----------------------------------------------------------------------|--------------------------------------------------|------------|------|

| $R_{\Theta ja}^{(1)}$                                                 | Junction-to-ambient thermal resistance           | 43         | °C/W |

| $\psi_{JT}$ <sup>(1)</sup> Junction-to-top characterization parameter |                                                  | 3          | °C/W |

| $R_{\Theta ja-EVM}$                                                   | Junction-to-ambient thermal resistance on LENEVM | 26         | °C/W |

(1) Measurements are based on standard 2s2p PCB defined in JESD 51-7 2s2p, under no wind, 2W loss, and 25°C ambient temperature.

### 7.5 Electrical Characteristics

Unless otherwise stated, the minimum and maximum limits apply over the recommended operating junction temperature range of -40°C to 150°C. Typical values are measured at 25°C and represent the most likely norm. The default conditions apply: VIN = 13.5V.

| SYMBOL               | PARAMETER                                                                    | CONDITIONS                                                                                         | MIN | ТҮР  | ΜΑΧ | UNIT |

|----------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----|------|-----|------|

| VIN, VOUT            | ↓<br>(VIN, VOUT, GND PINS)                                                   |                                                                                                    |     |      |     |      |

| V <sub>IN</sub>      | Operating Input Voltage<br>Range                                             |                                                                                                    | 3   |      | 40  | v    |

| I <sub>OUT</sub>     | Output current                                                               | $V_{\text{OUT}}$ in regulation                                                                     | 0   |      | 300 | mA   |

| I <sub>SHDN</sub>    | Input Shutdown Current                                                       | V <sub>EN</sub> = 0V                                                                               |     | 1.5  | 4.3 | μΑ   |

|                      | Input Quiescent Current<br>(Only LDO)                                        | $V_{EN} = 5V$ , $I_{OUT} = 0A$ ,<br>measured on GND pin.                                           |     | 16   | 32  | μΑ   |

|                      | Input Quiescent Current with WD Function                                     | $V_{EN} = 5V$ , $I_{OUT} = 0A$ , $V_{WEN} = 5V$ , measured on GND pin.                             |     | 22   | 40  | μΑ   |

| lα                   | Input Quiescent Current with V <sub>BAT</sub> Function                       | $V_{EN} = 5V$ , $I_{OUT} = 0A$ , $V_{SI} = 5V$ , $V_{BEN} = 5V$ , measured on GND pin.             |     | 18   | 34  | μΑ   |

|                      | Input Quiescent Current<br>with WD Function and<br>V <sub>BAT</sub> Function | $V_{EN} = 5V, I_{OUT} = 0A, V_{SI} = 5V,$<br>$V_{WEN} = 5V, V_{BEN} = 5V,$<br>measured on GND pin. |     | 24   | 42  | μΑ   |

| REGULATIO            | N (VOUT PIN)                                                                 | · · ·                                                                                              |     |      |     |      |

|                      | Regulated Output<br>Voltage Error for Fixed<br>V <sub>OUT</sub> Parts        | $40V > V_{IN} > V_{OUT} + 1V,$ $I_{OUTMAX} > I_{OUT} > 1mA$                                        | -2  |      | 2   | %    |

| V <sub>OUT</sub> %   | Line Regulation                                                              | $40V > V_{IN} > V_{OUT} + 1V,$<br>$I_{OUT} = 10 \text{ mA}$                                        |     | ±0.1 |     | %    |

|                      | Load Regulation                                                              | V <sub>IN</sub> = 13.5V,<br>I <sub>OUTMAX</sub> > I <sub>OUT</sub> > 1mA                           |     | ±0.5 |     | %    |

| DROP OUT             |                                                                              |                                                                                                    |     |      |     |      |

| V <sub>DO-5V</sub>   | Drop Out Voltage @<br>300mA                                                  | I <sub>OUT</sub> = 300mA, V <sub>IN</sub> = 5.1V,<br>V <sub>OUT-NOM</sub> = 5V                     |     | 300  | 550 | mV   |

| V <sub>DO-3.3V</sub> | Drop Out Voltage @<br>300mA                                                  | I <sub>OUT</sub> = 300mA, V <sub>IN</sub> = 3.4V,<br>V <sub>OUT-NOM</sub> = 3.3V                   |     | 430  | 750 | mV   |

| OVER CURP            | RENT PROTECTION                                                              |                                                                                                    |     |      |     |      |

| I <sub>limit</sub>   | Current Limit Threshold                                                      | V <sub>IN</sub> = 6V to 40V,<br>V <sub>OUT</sub> = 90%*V <sub>OUT-NOM</sub>                        | 301 | 430  | 650 | mA   |

# **Electrical Characteristics (Continued)**

| SYMBOL                  | PARAMETER                                                   | CONDITIONS                                                | MIN   | ТҮР                | MAX   | UNIT |

|-------------------------|-------------------------------------------------------------|-----------------------------------------------------------|-------|--------------------|-------|------|

| POWER SUI               | PPLY REJECTION RATIO (PSR                                   | k)                                                        |       |                    |       |      |

| Gpsrr-100Hz             | PSRR@100Hz                                                  | I <sub>OUT</sub> = 50mA, V <sub>OUT</sub> = 5V or<br>3.3V |       | 60 <sup>(1)</sup>  |       | dB   |

| Gpsrr-1kHz              | PSRR@1kHz                                                   | I <sub>OUT</sub> = 50mA, V <sub>OUT</sub> = 5V or<br>3.3V |       | 50 <sup>(1)</sup>  |       | dB   |

| Gpsrr-100kHz            | PSRR@100kHz                                                 | I <sub>OUT</sub> = 50mA, V <sub>OUT</sub> = 5V or<br>3.3V |       | 30 (1)             |       | dB   |

| ENABLE (EN              | I PIN)                                                      |                                                           |       |                    |       |      |

| $V_{\text{EN-H}}$       | EN Enable Threshold<br>Voltage                              |                                                           | 1.352 | 1.47               | 1.588 | v    |

| V <sub>EN-L</sub>       | EN Disable Threshold<br>Voltage                             |                                                           | 1.187 | 1.237              | 1.287 | v    |

| I <sub>EN-H</sub>       | EN Leakage Current                                          | V <sub>EN</sub> = 5V                                      |       | 1                  | 2     | μA   |

| THERMAL S               | HUTDOWN                                                     |                                                           |       |                    |       |      |

| T <sub>SD</sub>         | Thermal Shutdown<br>Threshold                               |                                                           | 151   | 164 <sup>(1)</sup> |       | °C   |

| T <sub>SD-HYS</sub>     | Thermal Shutdown<br>Recovery Hysteresis                     |                                                           |       | 16 <sup>(1)</sup>  |       | °C   |

| V <sub>BAT</sub> SENSE  |                                                             |                                                           |       |                    |       |      |

| V <sub>SI-H</sub>       | V <sub>BAT</sub> Under-Voltage<br>Reference Voltage Rising  |                                                           | 1.181 | 1.237              | 1.293 | V    |

| V <sub>SI-L</sub>       | V <sub>BAT</sub> Under-Voltage<br>Reference Voltage Falling |                                                           | 1.067 | 1.1                | 1.133 | v    |

| I <sub>SI</sub>         | SI Leakage Current                                          | V <sub>SI</sub> = 5V                                      | -150  |                    | 150   | nA   |

| $V_{\text{BEN-H}}$      | V <sub>BAT</sub> Sense Enable High-<br>Level Voltage        |                                                           | 2     |                    |       | v    |

| V <sub>BEN-L</sub>      | V <sub>BAT</sub> Sense Enable Low-<br>Level Voltage         |                                                           |       |                    | 0.7   | v    |

| I <sub>BEN-H</sub>      | BEN Leakage Current                                         | V <sub>BEN</sub> = 5V                                     |       | 1                  | 2     | μA   |

| R <sub>BO</sub>         | BO MOSFET On<br>Resistance                                  | V <sub>BEN</sub> = 5V, V <sub>EN</sub> = 5V               |       | 125                | 260   | Ω    |

| R <sub>BO-DN</sub>      | BO Pull-Down Resistor<br>When Disabled                      | $V_{BEN} = 0V, V_{BO} = 1V, V_{EN} = 5V \text{ or } 0V$   |       | 40                 | 64    | kΩ   |

|                         | SO Internal Pull-Down                                       | V <sub>EN</sub> = 5V, V <sub>SO</sub> = 1V                |       | 170                | 220   | Ω    |

| R <sub>SO-DN</sub>      | Resistance When Battery<br>Detected                         | V <sub>EN</sub> = 0V, V <sub>SO</sub> = 1V                |       | 203                | 260   | Ω    |

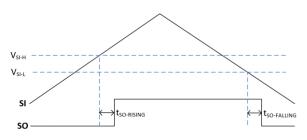

| t <sub>so-rising</sub>  | V <sub>BAT</sub> Sense Delay time                           |                                                           |       | 5                  |       | μs   |

| t <sub>so-falling</sub> | V <sub>BAT</sub> Sense Deglitch time                        |                                                           |       | 2.5                |       | μs   |

# Electrical Characteristics (Continued)

| SYMBOL                | PARAMETER                                             | CONDITIONS                       | MIN | ТҮР   | ΜΑΧ  | UNIT |

|-----------------------|-------------------------------------------------------|----------------------------------|-----|-------|------|------|

| WATCHDO               | G                                                     |                                  |     |       |      |      |

| I <sub>CS-CHG</sub>   | Delay Capacitor WD<br>Charge Current                  | Measured on delay pin.           | 3.1 | 4.4   | 6.2  | μΑ   |

| I <sub>CS-DHG</sub>   | Delay Capacitor WD<br>Discharge Current               | Measured on delay pin.           | 30  | 46    | 68   | μΑ   |

| V <sub>DH</sub>       | DELAY Pin High<br>Threshold Under WD<br>Monitor       | Measured on delay pin.           |     | 1.237 |      | v    |

| V <sub>DL</sub>       | DELAY Pin Low<br>Threshold Under WD<br>Monitor        | Measured on delay pin.           |     | 0.35  |      | v    |

| $V_{\text{D-HYS}}$    | DELAY Pin Threshold<br>Hysteresis Under WD<br>Monitor | Measured on delay pin.           | 0.8 | 0.887 | 0.95 | v    |

| V <sub>WD-H</sub>     | WDI/WEN High-Level<br>Voltage                         |                                  | 2   |       |      | v    |

| $V_{\text{WD-L}}$     | WDI/WEN Low-Level<br>Voltage                          |                                  |     |       | 0.7  | V    |

| I <sub>WD</sub>       | WDI/WEN input current                                 | WDI/WEN = 5V                     |     | 1     | 2    | μA   |

| t <sub>WDI</sub>      | Minimum WDI Pulse                                     | Both WDI High and Low pulses     | 5   |       |      | μs   |

| POWER GO              | OD                                                    |                                  |     |       |      |      |

| %V <sub>UV-RISE</sub> | UV Rising Threshold                                   | V <sub>OUT</sub> Ramping Up      | 80  | 88    | 96   | %    |

| %V <sub>UV-FALL</sub> | UV Falling Threshold                                  | Vout Ramping Down                | 77  | 85    | 93   | %    |

| %V <sub>OV-RISE</sub> | OV Rising Threshold                                   |                                  | 104 | 107   | 110  | %    |

| %V <sub>OV-FALL</sub> | OV Falling Threshold                                  |                                  | 102 | 105   | 108  | %    |

| I <sub>CS-ST</sub>    | Delay Capacitor PG<br>Charge Current                  | Measured on delay pin.           | 28  | 42    | 62   | μΑ   |

| V <sub>D-CLAMP</sub>  | Delay Voltage Clamping<br>Threshold                   |                                  |     | 4.7   |      | V    |

| D                     | RESET Internal Pull-                                  | EN = 5V, V <sub>RESET</sub> = 1V |     | 170   | 220  | Ω    |

| R <sub>reset-dn</sub> | Down Resistance When<br>Fault Happened                | EN = 0V, V <sub>RESET</sub> = 1V |     | 203   | 260  | Ω    |

(1) Not subject to production test, specified by design.

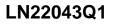

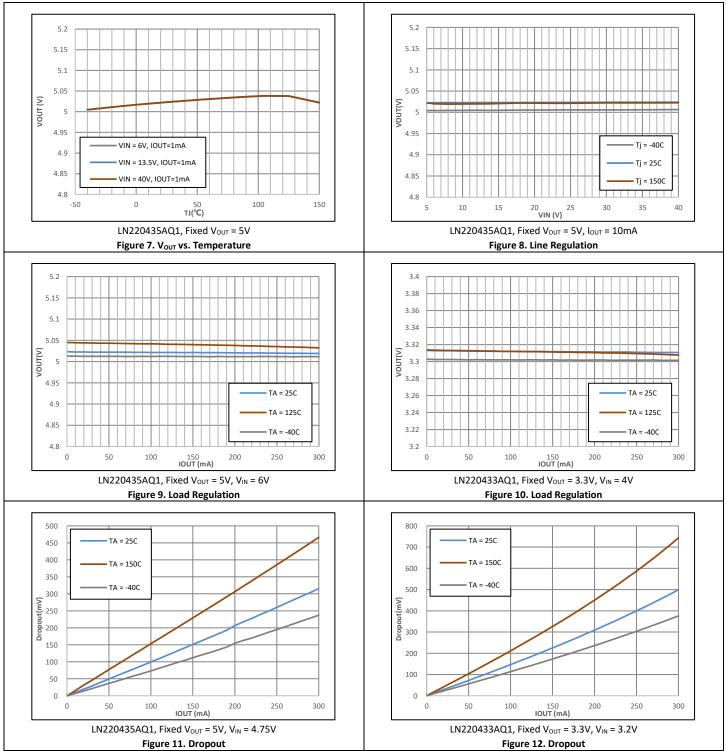

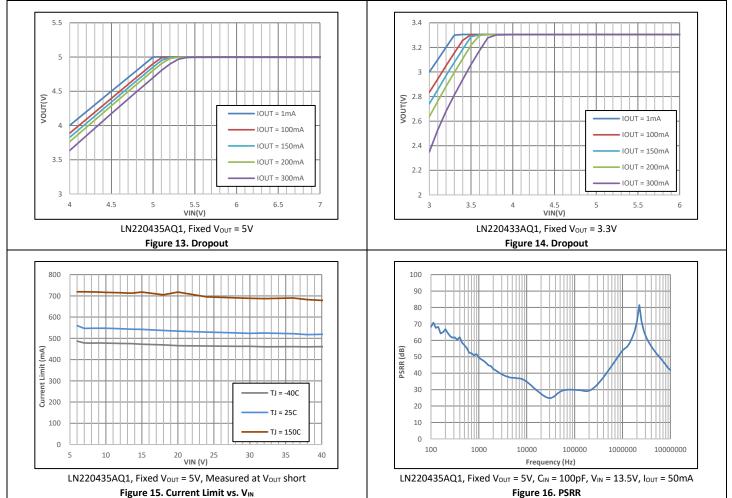

### 7.6 Typical Characteristics

#### 7.6.1 Characteristics Over Temperature

Unless otherwise stated, the test conditions are the same as Chapter 7.5.  $T_A = 25^{\circ}C$ .

### **Characteristics Over Temperature (Continued)**

Unless otherwise stated, the test conditions are the same as Chapter 7.5.  $T_A = 25$  °C.

### **Characteristics Over Temperature (Continued)**

Unless otherwise stated, the test conditions are the same as Chapter 7.5.  $T_A$  = 25  $^\circ\text{C}.$

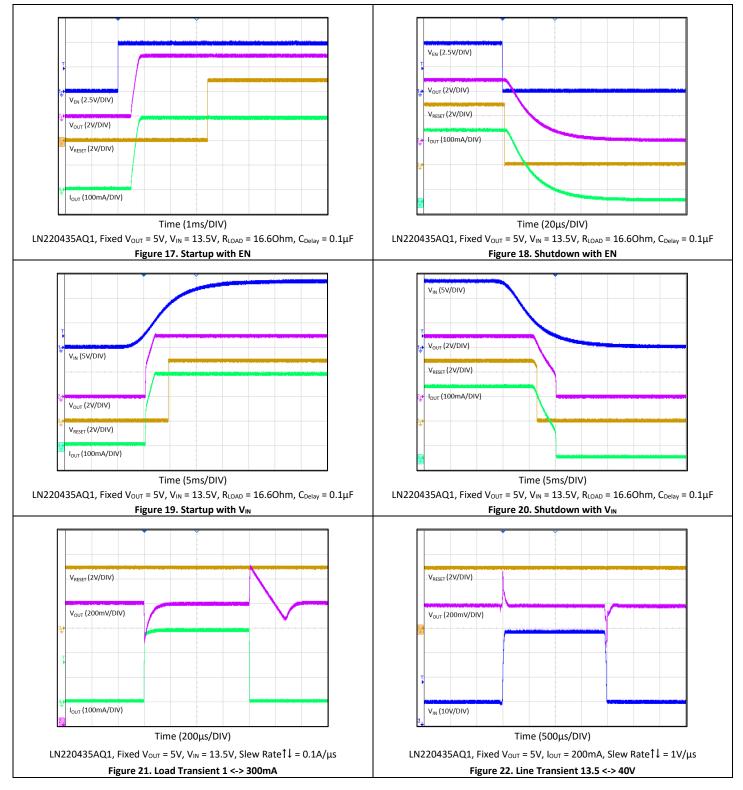

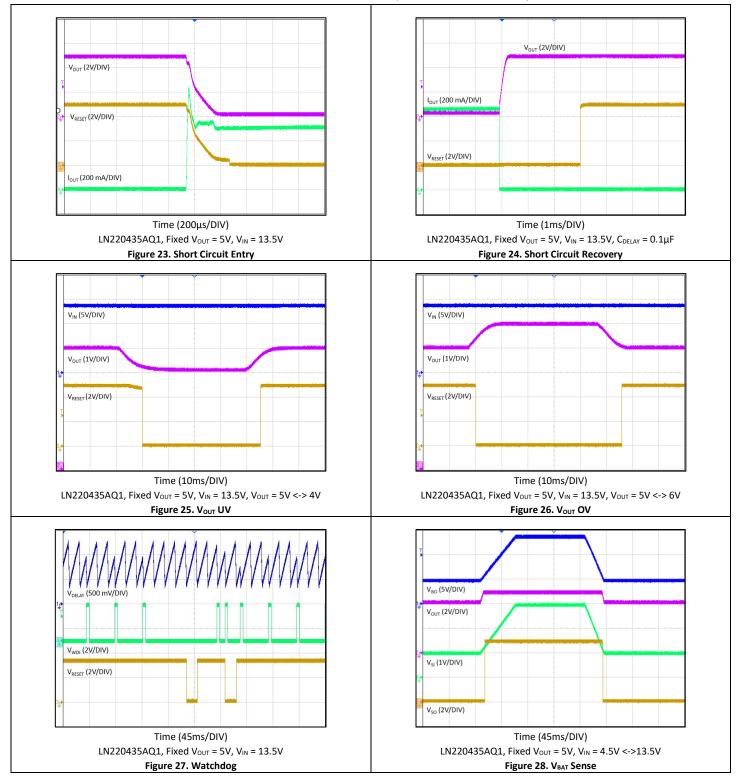

#### 7.6.2 Typical Waveforms

Unless otherwise stated, the test conditions are the same as Chapter 7.5.  $C_{IN} = C_{OUT} = 1\mu F$ ,  $T_A = 25^{\circ}C$ .

### **Typical Waveforms (Continued)**

Unless otherwise stated, the test conditions are the same as Chapter 7.5.  $C_{IN} = C_{OUT} = 1\mu F$ ,  $T_A = 25^{\circ}C$ .

### 8 Functional Description

#### 8.1 Overview

LN22043Q1 is a low quiescent current, low dropout linear regulator (LDO) with a wide input voltage range of 3V to 40V. The series provides fixed 3.3V or 5V outputs and delivers up to 300mA output current. Typical shutdown current of LN22043Q1 is less than 1.5µA, while the quiescent current under no-load condition is 16µA.

Watchdog function can provide an independent monitor for microcontrollers. Window watchdog mode can monitor whether the frequency of watchdog service signal (WDI) is within a preset range. Different fault conditions of missing pulse in open window and receiving pulse in close window can both be reported on RESET pin. The duration of watchdog window can be set by delay capacitor.

LN22043Q1 provides a battery voltage sense function. By integrating an independent switch and a dedicated BEN pin, V<sub>BAT</sub> sense function can be achieved by a simple peripheral circuit, without sacrificing system quiescent consumption.

LN22043Q1 also features power good indicator, over current protection and over temperature shutdown with auto restart.

The product family are available in DFN12(3X3) package with wettable flanks.

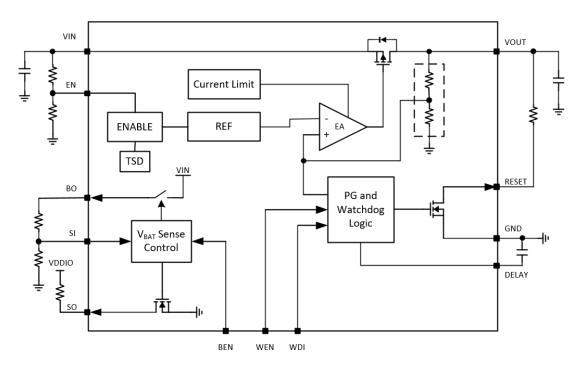

### 8.2 Funtional Dragram

Figure 29. LN22043Q1 Functional Diagram

#### 8.3 Funtional Description

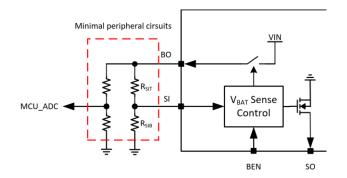

#### 8.3.1 Vbat Sense Function

LN22043Q1 provides a battery voltage sense function. By integrating an independent switch and a dedicated BEN pin, V<sub>BAT</sub> sense function can be achieved by a simple peripheral circuit, without sacrificing system quiescent consumption.

Only one or two pairs of resistor divider is needed to implement battery voltage sense, working procedures are described as follows, and schematic is shown in figure 30.

- 1) When BEN is enabled, BO pin is pullup to VIN though an internal switch.

- 2) V<sub>BAT</sub> can be sensed by connecting a voltage divider between BO and GND and connect the center of the divider to SI pin. When the SI voltage drops below threshold V<sub>SI-L</sub>, battery under-voltage is reported, and the SO will be pulled low. The use of external voltage divider makes this function very flexible in the applications. V<sub>IN</sub> rising threshold:

$$V_{IN-R} = \left(1 + \frac{R_{SIT}}{R_{SIB}}\right) \times V_{SI-H} \tag{1}$$

$V_{IN}$  falling threshold:

$$V_{IN-F} = \left(1 + \frac{R_{SIT}}{R_{SIB}}\right) \times V_{SI-L} \tag{2}$$

- Another pair of voltage divider can also be connected to BO pin and the divided signal can be connected an ADC of MCU for precise analog sensing.

- 4) Extreme low system IQ can be achieved by turning off BO pin through BEN.

Figure 30. V<sub>BAT</sub> Sense Function

The typical timing for SI comparator is shown in figure 31.

Figure 31. SI Timing

N LEN Technology LTD.

#### 8.3.2 Watchdog Function

#### 8.3.2.1 Function Description

Independent watchdog is a basic requirement in most reliable systems, which can provide an independent monitor circuit for microcontrollers, and reset MCU when software runaway. Window watchdog integrated in LN22043Q1 can monitor whether the frequency of watchdog service signal (WDI) is within a preset range.

In window watchdog mode, there is a close window and an open window, WDI signal must be served in the open window; Missing pulse in open window and receiving pulse in close window can both trigger fault window and be reported on RESET pin. The duration of watchdog window can be set by delay capacitor.

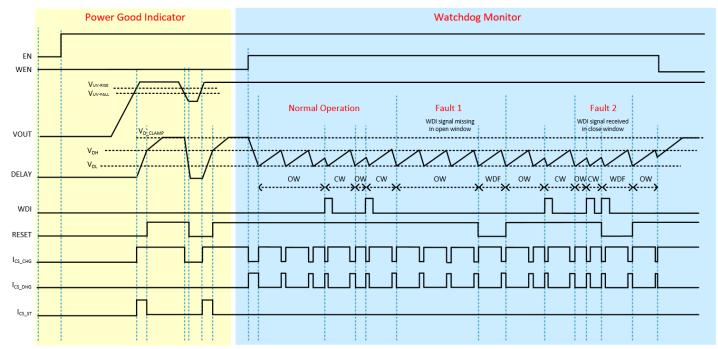

The operation of window watchdog is descripted as follow, and the timing diagram of watchdog is shown in Figure 32.

- 1) When watchdog function is enabled through WEN pin, voltage on DELAY pin is discharged from V<sub>D-CLAMP</sub> to V<sub>DL</sub>, it enters open window status, and then DELAY pin begins to charge and discharge.

- 2) When WDI pin detects a trigger in open window, it switches to close window immediately, and then a complete cycle of charge and discharge procedure is implemented on DELAY pin, the voltage goes from V<sub>DL</sub> to V<sub>DH</sub> and then back to V<sub>DL</sub>. During the close window, WDI must keep quiet.

- 3) After the closed window, the watchdog will come back to the open window status again and wait for the next WDI signal. When the next WDI signal comes, it will go back to step 2), and the procedure repeats.

- 4) Two types of faults can be reported during above procedure: Fault 1: The WDI signal is not received during the open window; watchdog turns to fault window after open window complete and reports low signal on RESET pin, the time duration of RESET low voltage equals one complete cycle to make sure MCU is properly reset. After the fault window, watchdog will go back to open window and repeat step 2). Fault 2: The WDI signal is received during the close window, it enters fault window immediately, the voltage on the DELAY pin is discharged to V<sub>DL</sub> first and then followed by a complete cycle of charge and discharge procedure. The

After the fault window, watchdog will go back to open window and repeat step 2).

5) After watchdog function is disabled, voltage on DELAY pin is charged to V<sub>D-CLAMP</sub> and RESET will not be pulled low due to failed WDI signal.

time duration of RESET low voltage may be a little longer than one complete cycle depends on the WDI signal position.

#### 8.3.2.2 Watchdog timing

#### Figure 32. Window Watchdog

#### 8.3.2.3 Calculation of Timing

The duration of the watchdog window can be programmed by connecting an external capacitor to ground at the DELAY pin. Voltage on the DELAY pin will be charged and discharged repeatedly between  $V_{DH}$  and  $V_{DL}$ . Close window lasts for about one charging and discharging cycle, while open window is three cycles, so the ratio between open window and closed window duration is fixed as 3:1. Different capacitance will influence the charging and discharging time, and then determine the watchdog period.

The voltage difference between  $V_{\text{DH}}$  and  $V_{\text{DL}}$  is defined as  $V_{\text{D-HYS}}.$

$$V_{D-HYS} = V_{DH} - V_{DL} \tag{3}$$

Open window lasts for 3 charging and discharging cycles, so the duration is:

$$t_{OW} = 3 \times V_{D-HYS} \times C_{delay} \times \left(\frac{1}{I_{CS-CHG}} + \frac{1}{I_{CS-DHG}}\right)$$

(4)

Close window duration maybe a little different depends on the WDI signal position. If WDI signal occurs when the DELAY pin volage is V<sub>DL</sub>, then the close window duration is one complete charging and discharging period, the minimum close window duration is:

$$t_{CW-MIN} = V_{D-HYS} \times C_{delay} \times \left(\frac{1}{I_{CS-CHG}} + \frac{1}{I_{CS-DHG}}\right)$$

(5)

LEN Technology LTD.

While if the WDI occurs when the DELAY pin volage is at  $V_{DH}$ , then the close window should go through a discharging time first, and then followed by another charging and discharging period. So, the maximum close window duration is:

$$t_{CW-MAX} = V_{D-HYS} \times C_{delay} \times \left(\frac{1}{I_{CS-CHG}} + \frac{1}{I_{CS-DHG}} + \frac{1}{I_{CS-DHG}}\right)$$

(6)

After WDI signal is effectively triggered, to avoid a watchdog fault, the next WDI signal must come after the maximum close window, and before the open window time out, so the period of the WDI signal should be in below range.

$$t_{CW-MAX} < t_{WDI} < t_{OW} + t_{CW-MIN} \tag{7}$$

Taking the spec variation of the device and capacitor into consideration, the recommended WDI signal period can be set as two complete charge and discharge cycles, then the watchdog WDI signal period and frequency are calculated as below:

$$t_{WDI-NOM} = 2 \times V_{D-HYS} \times C_{delay} \times \left(\frac{1}{I_{CS-CHG}} + \frac{1}{I_{CS-DHG}}\right)$$

(8)

$$f_{WDI-NOM} = \frac{1}{t_{WDI-NOM}} = \frac{1}{2 \times V_{D-HYS} \times C_{delay} \times \left(\frac{1}{I_{CS-CHG}} + \frac{1}{I_{CS-DHG}}\right)}$$

(9)

If something is wrong with the MCU, and WDI comes within the close window or after the open window, the watchdog fault is triggered, RESET pin will be pulled to low. Depends on when the fault happens, the fault window duration is a little different which is similar to the close window calculation method.

$$t_{WDF-MAX} = V_{D-HYS} \times C_{delay} \times \left(\frac{1}{I_{CS-CHG}} + \frac{1}{I_{CS-DHG}} + \frac{1}{I_{CS-DHG}}\right)$$

(10)

$$t_{WDF-MIN} = V_{D-HYS} \times C_{delay} \times \left(\frac{1}{I_{CS-CHG}} + \frac{1}{I_{CS-DHG}}\right)$$

(11)

#### 8.3.3 V<sub>OUT</sub> UV and OV Monitor Function

The RESET pin is open drain output, so the RESET pin needs to be pulled up to a voltage source by a resistor externally. When  $V_{OUT}$  is not in the desired range, RESET pin outputs low voltage to reset MCU.

When EN is high and  $V_{OUT}$  rises above the power good threshold  $V_{UV-RISE}$ , to make sure that MCU is properly reset, the RESET pin isn't pulled up directly. Instead, the DELAY pin starts to output a current ( $I_{CS-CHG}$ +  $I_{CS-ST}$ ) to charge the external delay capacitor, only after the voltage on the DELAY pin rises across  $V_{DH}$ , RESET is pulled up.

The external delay capacitor is selected based on the desired MCU delay time t<sub>Delay</sub> and is calculated based on:

$$C_{\text{Delay}} = \frac{(I_{CS-CHG} + I_{CS-ST}) \times t_{\text{Delay}}}{V_{\text{DH}}}$$

(12)

When EN is high but  $V_{OUT}$  is below the power good threshold  $V_{UV-FALL}$ , the DELAY pin will discharge the voltage of delay capacitor within microsecond level through an internal resistor, and after the voltage on the DELAY pin is below  $V_{DL}$ , RESET is pulled down.

21

\_\_\_\_

LN22043Q1 also integrates an over voltage monitor function. When  $V_{OUT}$  rises above the threshold  $V_{OV-RISE}$ , the DELAY pin also will quickly discharge the DELAY pin to  $V_{DL}$  and then RESET is pulled down. When the OV state disappears, the DELAY pin will be recharged to  $V_{DH}$  and then the RESET pin will be released again.

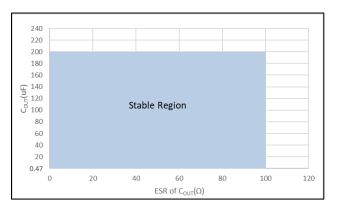

#### 8.3.4 Output capacitor stable region

LN22043Q1 can operate stably in the wide range of 0.47 uF to 200 uF and 0 $\Omega$  to 100 $\Omega$  of equivalent resistance (ESR).

Figure 33. Stable Region

#### 8.3.5 Accurate EN control

An accurate threshold is placed at  $V_{EN-H}$ , when EN voltage rises above this threshold, it turns on the LDO. This accurate threshold serves to provide an accurate system  $V_{IN}$  UVLO level. In the application, an enable divider can be added between VIN and GND. The LDO can thus be turned on and off at programmable precise input voltages. The  $V_{IN}$  UVLO threshold can be determined by:

$$V_{IN-Rising} = \left(1 + \frac{R_{ENT}}{R_{ENB}}\right) \times V_{EN-H}$$

(13)

$$V_{IN-Falling} = \left(1 + \frac{R_{ENT}}{R_{ENB}}\right) \times V_{EN-L}$$

(14)

#### 8.3.6 Over-Current Protection

LN22043Q1 features over-current protection to keep the device in a safe operating area when the circuit overload or output short to ground. When the over-current protection is triggered, the device output current is clamped to the current limit.

#### 8.3.7 Thermal Shutdown and Auto-Recovery

LN22043Q1 features thermal shutdown and auto-recovery as a protection from over-heating. When the junction temperature exceeds 164°C, the device turns off the output to reduce thermal dissipation. It automatically restarts the output after junction temperature drops back below 148  $^{\circ}$ C.

### 9 Typical Applications

#### 9.1 Application Diagram with Full Features

Figure 34. Typical Application

#### 9.2 Design Requirements

For this design example, use the parameters listed in table 1 as the input parameters.

#### **Table 1 Design Parameters**

| Design Parameter                         | Example Value |

|------------------------------------------|---------------|

| Input voltage range                      | 6V to 16V     |

| Output voltage                           | 5V            |

| Output current                           | 200mA         |

| V <sub>IN</sub> startup threshold        | 5.5V          |

| V <sub>BAT</sub> Sense falling threshold | 6V            |

| Power good delay time                    | 2.5ms         |

#### 9.3 Detailed Design Procedure

The following design procedure applies to Figure 34 and Table 1.

#### 9.3.1 R<sub>ENT</sub> and R<sub>ENB</sub> Select

When the system confirms the V<sub>IN</sub> startup threshold, use equation (15) to calculate the value of R<sub>ENT</sub> to R<sub>ENB</sub>.

$$R_{ENT} = \left(\frac{V_{IN-Rising}}{V_{EN-H}} - 1\right) \times R_{ENB}$$

(15)

Where  $V_{\text{IN-Rising}}$  is the  $V_{\text{IN}}$  startup threshold.

To reduce the input quiescent current, the recommended resistance value of  $R_{ENB}$  is between  $100k\Omega$  to  $1M\Omega$ . For example, if the  $R_{ENB}$  select a resistance of  $510k\Omega$ , then the  $R_{ENT}$  requires the selection of a  $1.4M\Omega$  resistance. Use equation (14) to calculate the  $V_{IN-Falling}$  threshold is 4.6V.

#### 9.3.2 R<sub>SIT</sub> and R<sub>SIB</sub> Select

When the system confirms the sense input trip threshold, use equation (16) to calculate the value of R<sub>SIT</sub> to R<sub>SIB</sub>.

$$R_{SIT} = \left(\frac{V_{IN-F}}{V_{SI-L}} - 1\right) \times R_{SIB}$$

(16)

Where  $V_{IN-F}$  is the target  $V_{BAT}$  falling threshold.

Typically,  $R_{SIB}$  is recommended to choose a resistance between  $10k\Omega$  to  $1M\Omega$ . For example, if the  $R_{SIB}$  select a resistance of 24.9k $\Omega$ , then  $R_{SIT}$  requires the selection of a  $110k\Omega$  resistance. Use equation (1) to calculate the SO error clearance threshold is 6.7V.

#### 9.3.3 Power Good Delay Capacitor Select

When the system confirms the PG delay time, use equation (12) to calculate the PG delay capacitor.

$$C_{\text{Delay}} = 93.8nF$$

Considering the derating of the capacitor, the recommended PG delay capacitor is 100nF.

#### 9.3.4 Calculation of Watchdog Serve Frequency

After confirming the PG delay capacitor, use equation (8)  $\sim$  (9) to calculate the recommended watchdog WDI signal period and frequency.

Use equation (8) to calculate the recommended WDI signal period:

$t_{WDI-NOM} = 44.2ms$

Use equation (9) to calculate the recommended WDI signal frequency:

$$f_{WDI-NOM} = 22.64Hz$$

Please note that both PG delay time and watchdog period are determined by delay capacitor, it is not necessary to calculate the  $C_{Delay}$  by PG delay time, if the WDI frequency is more important, then users can also use equation (8) ~ (9) to choose the capacitor value first and calculate the PG delay time later. Sometimes users must make a tradeoff between the two specifications.

#### 9.3.5 Estimating Junction Temperature

The power dissipation for the regulator is calculated as below:

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT} \tag{17}$$

For the application of the 16V maximum input voltage, the maximum power dissipation for the regulator is 2.2W. Referring to chapter 7.4, the thermal resistance of the LEN EVM is 26°C/W. The junction temperature calculation equation is as below:

$$\Delta T_{Rise} = P_D \times R_{\theta JA-EVM} \tag{18}$$

Use equation (18) to calculate the maximum temperature rising is 57.2°C. The regulator can operate at maximum temperature of 85°C without triggering over temperature protection.

# 10 Layout

### 10.1 Layout Guidelines

To minimize the impact of parasitic parameters and improve the PSRR, EMC and thermal performance, it is recommended the following layout principles are applied to LN22043Q1 series products.

| Number | Name        | Layout Guideline                                                                                                                                                                                                                |

|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VIN         | Place a ceramic capacitor $C_{IN}$ of at least 1µF between VIN and GND. $C_{IN}$ should be as close as possible to the VIN and GND pins. An additional ceramic capacitor in small package (such as 0603) is highly recommended. |

| 2      | EN          | Connect to VIN directly, to VIN through a divider, or to a logic control signal.                                                                                                                                                |

| 3      | BO          | Connect to SI divider. If not used, keep this pin floating.                                                                                                                                                                     |

| 4      | SI          | Connect to the center leg of the voltage divider between BO and GND. The ground connection of voltage divider should be located to GND pin as close as possible. If not used, connect to the BO pin.                            |

| 5      | GND         | It is recommended to connect to a GND plane.                                                                                                                                                                                    |

| 6      | DELAY       | Place a ceramic capacitor between DELAY and GND. The capacitor should be as close as possible to DELAY and GND pins. If not used, keep this pin floating.                                                                       |

| 7      | RESET       | Connect to a voltage not greater than $V_{OUT}$ through a pull-up resistor. If not used, left this pin floating is recommended.                                                                                                 |

| 8      | so          | Connect to a voltage not greater than $V_{OUT}$ through a pull-up resistor. If not used, left this pin floating is recommended.                                                                                                 |

| 9      | BEN         | Connect to the MCU GPIO interface.                                                                                                                                                                                              |

| 10     | WEN         | Connect to the MCU GPIO interface.                                                                                                                                                                                              |

| 11     | WDI         | Connect to the MCU GPIO interface.                                                                                                                                                                                              |

| 12     | VOUT        | Place a ceramic capacitor $C_{OUT}$ of at least 0.47µF between VOUT and GND. $C_{OUT}$ should be as close as possible to the VOUT and GND pins.                                                                                 |

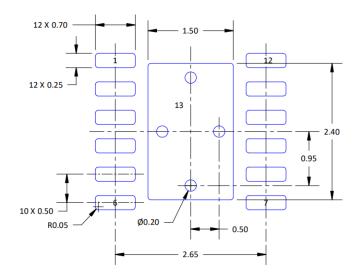

|        | Thermal pad | It is recommended to connect the thermal pad to a complete ground plane through<br>an array of 0.2mm thermal vias for heat sinking.                                                                                             |

### 10.2 Layout Example

♦ The vias connect to GND

OThe vias connect to signal

The vias under thermal pad and connect to GND

#### Figure 35. LN22043Q1 Layout Example

### 11 Package Information

#### 11.1 Package Outline

Notes:

- 1. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 2. Both package length and width do not include mold flash.

- 3. Unremoved flash between leads & package end flash shall not exceed 0.15mm from bottom body per side.

- 4. Features may not be present.

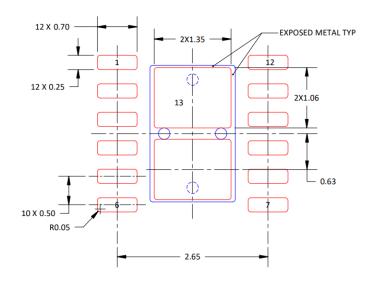

#### **11.2** Footprint Example

LAND PATTERN EXAMPLE EXPOSED METAL SHOWN SCALE:25X

SOLDER PASTE EXAMPLE BASED ON 0.125 mm THICK STENCIL FOR PAD 13 80% PRINTED SOLDER COVERAGE BY AREA SCALE:25X

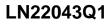

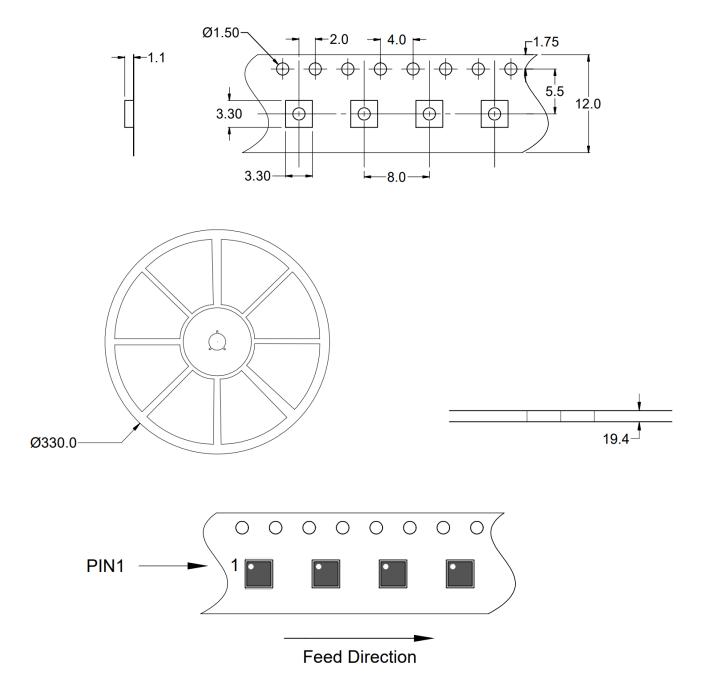

### **11.3** Tape and Reel Information

#### **Important Notice and Disclaimers**

The technical materials, reliability data, product specifications, and related product evaluation boards provided by LEN Technology Ltd. are on an "as is" basis. LEN Technology Ltd. is not responsible for any errors that may occur in these resources. LEN Technology Ltd. disclaims all expressed and implied warranties, including any implied warranties that the intellectual property rights of third parties will not be infringed.

These resources from LEN Technology Ltd. are provided only to those who have experience in developing electronic products. You will be solely responsible for selecting appropriate products from LEN Technology Ltd., and for verifying and testing your design to meet the standards of your application, as well as for any other safety and security requirements.

The resources provided by LEN Technology Ltd. are subject to change without notice. LEN Technology Ltd. Only grants you the rights for developing applications with the products of LEN Technology Ltd. described in these resources. Reproduction and display of these resources is prohibited. LEN Technology Ltd. does not grant any other intellectual property rights owned by LEN Technology Ltd. or any third-party licensed intellectual property. LEN Technology Ltd. does not assume any loss, cost and liabilities for the use of these resources.

### **Enviromental Declaration**

This product complies with the requirements of RoHS and REACH. In accordance with relevant Chinese regulations and standards, it does not contain toxic or harmful substances or elements.